Features: General

Compliant with ETS 300 421 for DVB, DVBS.

Compliant with ISO/IECCD 138181 MPEGII transport layer protocol.

Input code rate frequency up to 10 MBits/sec at 5V.

Onchip Bit Error Rate monitoring.

SEU immunity better than 30 MeV/mg/cm2

Total dose better than 50 Krad (Si).

Supply voltage 3 to 5V.

Power consumption 1W at 5V / 10MHz external clock frequency (code rate 7/8).

0.6m drawn CMOS, 3 metal layers.

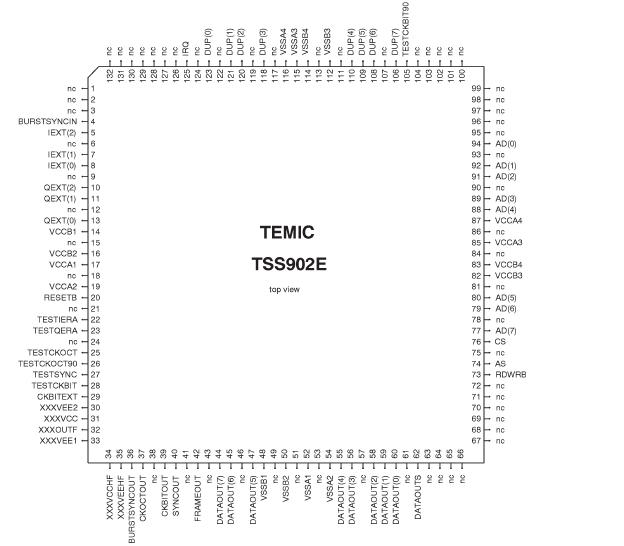

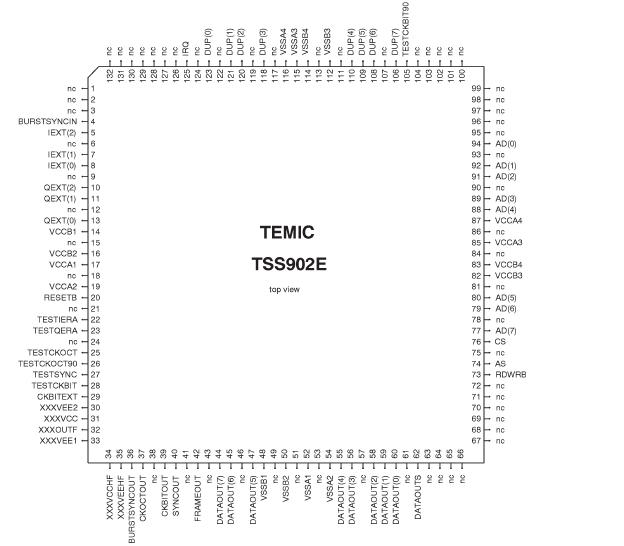

132pin MQFP.

Viterbi Decoder

Selectable code rates 1/2, 2/3, 3/4, 5/6 and 7/8 or automatic acquisition mode.

Hard decision or 3Bit softdecision decoder inputs.

Constraint length k = 7.

Eb/N0 for BER 2.104 (code rate 1/2) 3.5 dB.

Synchronization controller

Automatic synchronization capabilities for QPSK or BPSK.

Responds to inverted synchronization byte.

Programmable synchronization byte.

Convolutional deinterleaver

Error protected frame length n = 204.

Interleave depth I = 12.

Reed Solomon Decoder

Supported programmable shortened code length K = 34 to 239, T = 8.

Correction capability up to T = 8 bytes.

Descrambler (Energy Dispersal)

Polynomial generator q(x) = X15 + X14 + 1.

MPEGII inverted synchronization byte.Pinout SpecificationsStorage Temperature . . . . . . . . . . . . . . . . . . . .65 to +150°C

SpecificationsStorage Temperature . . . . . . . . . . . . . . . . . . . .65 to +150°C

Voltage on any other Pin to VSS . . . . . . . . . . .0.5 to +6.5 V

IOL per I/O Pin . . . . . . . . . . . . . . . . . . . . . . . . .0.5 to +6.5 V

Power Dissipation . . . . . . . . . . . . . . . . . . . . . .3 W

DescriptionDigital communication channels are inherently noisy, making transmission error control essential for reliable communication at low transmit power.

The TEMIC TSS902E is a singlechip Forward Error Correction decoder; it conforms to the MPEGII transport layer protocol specified by ISO/IEC standard and FEC requirements of Digital Video Broadcasting (DVB) specification; its typical applications are DVB satellites, regenerative multimedia transmission satellites and military communications.

The TEMIC TSS902E capabilities rely on Viterbi and ReedSolomon decoding algorithms to achieve extremely low biterror rate (BER) on the transmitted data. Allowing discontinuous data blocks transmission, the TSS902E burst mode feature is unique.

The component is made of the following blocks:

The inner decoder which performs the first level error detection and correction. This unit is made of a depuncturing block, a Viterbi decoder (k=7) and a synchronization/clock controller.

The convolutional deinterleaver, l=12 bytes for RS (204, 188, T=8) configuration.

The outer decoder performs the second level error protection, using a Reed Solomon (255, 239) error correcting process.

The descrambler for energy dispersal removal.

A microprocessor interface to setup the device and monitor the testability functions.

While monitoring the inner Viterbi decoder BER output, the phase and the depuncturing pattern are tuned until the Viterbi decoder proper alignment is found.

The Viterbi decoder output feeds the deinterleaver and ReedSolomon decoder synchronization module. Once the synchronization words have been found, the deinterleaver, the outer ReedSolomon decoder and the descrambler are properly aligned.

Each functional block may be bypassed, giving more flexibility to a system designer.

TSS902E Data Sheet

TSS902E Data Sheet