Features: 80C52 Compatible• 8051 pin and instruction compatible• Four 8-bit I/O ports• Three 16-bit timer/counters• 256 bytes scratchpad RAM

High-Speed Architecture• 40 MHz @ 5V, 30MHz @ 3V• X2 Speed Improvement capability (6 clocks/machine cycle)30 MHz @ 5V, 20 MHz @ 3V (Equivalent to60 MHz @ 5V, 40 MHz @ 3V)

Dual Data Pointer

On-chip ROM/EPROM (16K-bytes, 32K-bytes)

Programmable Clock Out and Up/Down Timer/Counter 2

Hardware Watchdog Timer (One-time enabled withReset-Out)

Asynchronous port reset

Interrupt Structure with• 6 Interrupt sources• 4 level priority interrupt system

Full duplex Enhanced UART• Framing error detection• Automatic address recognition

Low EMI (inhibit ALE)

Power Control modes• Idle mode• Power-down mode• Power-off Flag

Once mode (On-chip Emulation)

Power supply: 4.5-5.5V, 2.7-5.5V

Temperature ranges: Commercial (0 to 70oC) andIndustrial (-40 to 85oC)

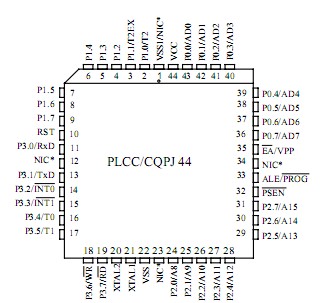

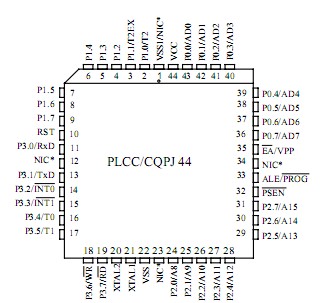

Packages: PDIL40, PLCC44, VQFP44 1.4, PQFP44F1, CQPJ44 (window), CDIL40 (window)

Pinout SpecificationsAmbiant Temperature Under Bias:

SpecificationsAmbiant Temperature Under Bias:

C = commercial 0°Cto70°C

I = industrial -40°Cto85°C

Storage Temperature -65°Cto+150°C

Voltage on VCC to VSS -0.5Vto+7V

Voltage on VPP to VSS -0.5Vto+13V

Voltage on Any Pin to VSS -0.5VtoVCC + 0.5 V

Power Dissipation 1 W(2)DescriptionTS80C54/58X2 is high performance CMOS ROM, OTPand EPROM versions of the 80C51 CMOS single chip8-bit microcontroller.

The TS80C54/58X2 retains all features of the AtmelWireless & Microcontrollers 80C51 with extendedROM/EPROM capacity (16/32 Kbytes), 256 bytes ofinternal RAM, a 6-source , 4-level interrupt system, anon-chip oscilator and three timer/counters.

In addition, the TS80C54/58X2 has a HardwareWatchdog Timer, a more versatile serial channel thatfacilitates multiprocessor communication (EUART) anda X2 speed improvement mechanism.

The fully static design of the TS80C54/58X2 allows toreduce system power consumption by bringing the clockfrequency down to any value, even DC, without loss ofdata.

The TS80C54/58X2 has 2 software-selectable modes ofreduced activity for further reduction in powerconsumption. In the idle mode the CPU is frozen whilethe timers, the serial port and the interrupt system are stilloperating. In the power-down mode the RAM is savedand all other functions are inoperative.

TS80C54X2 Data Sheet

TS80C54X2 Data Sheet