Features: ` Dual Output Voltages for Split-Supply pplications

` Selectable Power Up Sequencing for DSP pplications (See TPS704xx for

Independent Enabling of Each Output)

` Output Current Range of 1 A on

Regulator 1 and 2 A on Regulator 2

` Fast Transient Response

` Voltage Options Are 3.3-V/2.5-V, 3.3-V/1.8-V,3.3-V/1.5-V, 3.3-V/1.2-V, and Dual Adjustable Outputs

` Open Drain Power-On Reset With 120-ms elay

` Open Drain Power Good for Regulator 1

` Ultralow 185 A (typ) Quiescent Current

` 2 A Input Current During Standby

` Low Noise: 78 VRMS Without Bypass apacitor

` Quick Output Capacitor Discharge Feature

` Two Manual Reset Inputs

` 2% Accuracy Over Load and Temperature

` Undervoltage Lockout (UVLO) Feature

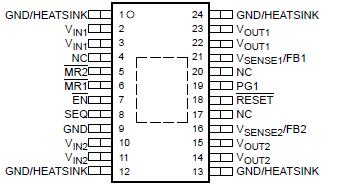

` 24-Pin PowerPAD™ TSSOP Package

` Thermal Shutdown ProtectionPinout Specifications

SpecificationsInput voltage range‡: VIN1 . . . . . . . . . . . . . . . . . . . . . . . 0.3 V to 7 V

VIN2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.3 V to 7 V

Voltage range at EN . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.3 V to 7 V

Output voltage range (VOUT1, VSENSE1) . . . . . . . . . . . . . . . . . . . .. 5.5 V

Output voltage range (VOUT2, VSENSE2) . . . . . . . .. . . . . . . . . . . . . 5.5 V

Maximum RESET, PG1 voltage . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . 7 V

Maximum MR1, MR2, and SEQ voltage . . . . . . . . . . . . . . . . . . .. . . . VIN1

Peak output current . . . . . . . . . . . . . . . . . . . . . . . . . . Internally limited

Continuous total power dissipation . . . . See Dissipation Rating Tables

Operating virtual junction temperature range, TJ . . .. . . 40 to 125

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . .65 to 150

ESD rating, HBM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . 2 kV

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and unctional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not mplied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

‡ All voltages are tied to network ground.

DescriptionThe TPS70302 voltage regulators offers very low dropout voltage and dual outputs with power up equence control, which is designed primarily for DSP applications. These TPS70302 have extremely low noise utput performance without using any added filter bypass capacitors and are designed to have a fast transient esponse and be stable with 10 uF low ESR capacitors.

These TPS70302 have fixed 3.3-V/2.5-V, 3.3-V/1.8-V, 3.3-V/1.5-V, 3.3-V/1.2-V, and adjustable/adjustable voltage ptions. The 3.3-V output regulator (regulator 1) can support up to 500 mA, and the other regulator (regulator ) can support up to 250 A. Separate voltage inputs allow the designer to configure the source power.

ecause the PMOS device TPS70302 behaves as a low-value resistor, the dropout voltage is very low (typically 170 mV n regulator 1) and is directly proportional to the output current. Additionally, since the PMOS pass element is voltage-driven device, the quiescent current of TPS70302 is very low and independent of output loading (maximum of 225 A over the full range of output current). This LDO family also features a sleep mode; applying a high signal to EN (enable) shuts down both regulators, reducing the input current to 1 A at TJ = 25°C.

The TPS70302 is enabled when the EN pin is connected to a low-level input voltage. The output voltages of the two egulators are sensed at the VSENSE1 and VSENSE2 pins respectively.

The input signal of TPS70302 at the SEQ pin controls he power-up sequence of the two regulators. When the device is enabled and the SEQ terminal is pulled high r left open, VOUT2 will turn on first and VOUT1 will remain off until VOUT2 reaches approximately 83% of it's egulated output voltage. At that time VOUT1 will be turned on. If VOUT2 is pulled below 83% (i.e. over load ondition) VOUT1 will be turned off. Pulling the SEQ terminal low, reverses the power-up order and VOUT1 will e turned on first. The SEQ pin is connected to an internal pullup current source.

For each regulator TPS70302, there is an internal discharge transistor to discharge the output capacitor when the regulator

is turned off(disabled).

The PG1 pin of TPS70302 reports the voltage conditions at the VOUT1, which can be used to implement a SVS (power on eset) for the circuitry supplied by regulator 1.

The TPS70302 features a RESET (SVS, POR, or power on reset). RESET is an active low, open drain output nd requires a pullup resistor for normal operation. When pulled up, RESET goes to a high impedance state i.e. logic high) after a 120 ms delay when all three of the following conditions are met. First, VIN1 must be above he undervoltage condition. Second, the manual reset (MR) pin must be in a high impedance state. Third, VOUT2 ust be above approximately 95% of its regulated voltage. To monitor VOUT1, the PG1 output pin can be onnected to MR1 or MR2. RESET can be used to drive power on reset or a low-battery indicator. If RESET s not used, it can be left floating.

Internal bias voltages of TPS70302 are powered by VIN1 and require 2.7 V for full functionality. Each regulator input has an ndervoltage lockout circuit that prevents each output from turning on until the respective input reaches 2.5 V.

TPS70302 Data Sheet

TPS70302 Data Sheet