Features: Single-Chip Multi-PHY Solution: Four 10BASE-T Physical-Layer (PHY) Interfaces in One Package Minimizing PCB Footprint for Internetworking Applications

Each PHY is Half-Duplex and Full-Duplex Compliant Full-Duplex: Independent Transmit and Receive Channels for Operation at 20-Mbit/s Aggregate

Compliant With IEEE Std 802.3 10BASE-T Specification

Management Data Input/Output (MDIO) Serial Compliant With IEEE Std 802.3 Media-Independent Interface (MII)

Integrated Filters on Both Receive and Transmit Circuits No External Filters Are Required Meets IEEE Std 802.3 (Section 14.3) Electrical Requirements

Implements IEEE Std 802.3u Auto-Negotiation to Establish the Highest Common Protocol

DSP-Based Digital Phase-Locked Loop (PLL)

Interrupt Feature on MDIO

Loopback Mode for Test Operations

Integrated Manchester Encoding/Decoding

Receive-Clock Regeneration for All Input Channels

Smart Squelch

Transmit Pulse Shaping

Collision Detection

Jabber Detection

Link-Pulse Detection

Auto-Polarity Control

Simple Connection for LED Status Indicators

Sufficient Current Drive to Directly Connect LED Status Indicators

CMOS Technology Enables Low Power Consumption

Power-Down Mode

IEEE Std 1149.1 (JTAG)† Test-Access Port (TAP)

Each Serial Network Interface (SNI) Signal Is User Programmable

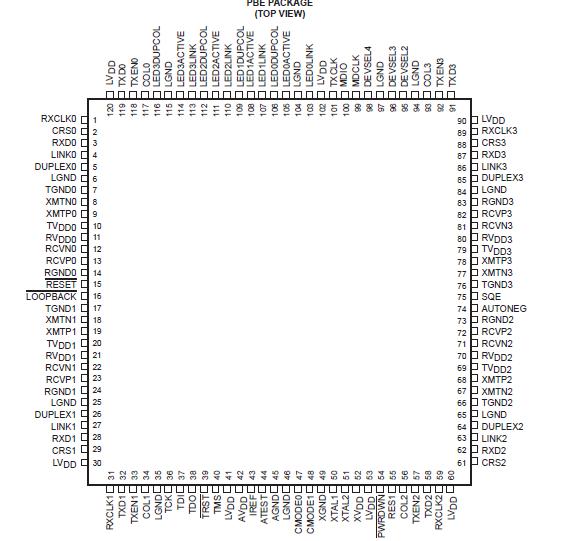

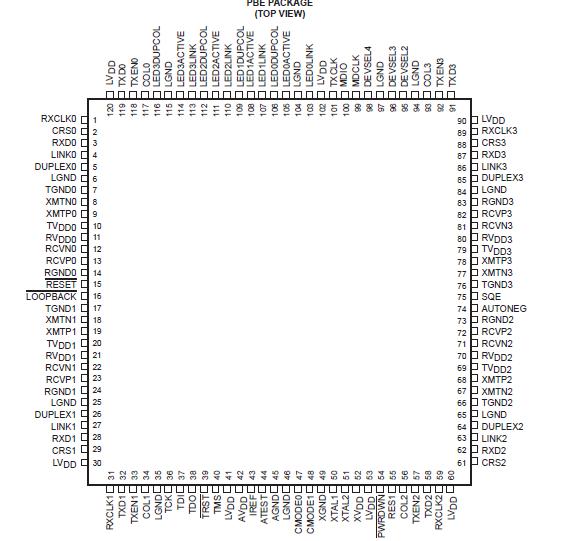

Package Options Include 120-Pin Plastic Quad Flat Package (PBE) and 128-Pin Plastic Quad Flat Package (PAC)Pinout

Specifications

SpecificationsNormal power-supply voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.0 V ± 5%

Power-supply current draw (see Note 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 510 mA

Power-supply current draw (see Note 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240 mA

dc voltage applied to logic outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.05 V to VCCMAX

dc voltage applied to logic input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.25 V

dc differential voltage at receiver pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 5 V

Input voltage range (see Note 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 5.25 V

Operating case temperature range, TC . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . 0°C to 95°C

RqJA (see Note 5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22°C/W

RqJA (see Note 6) . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27°C/W

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65°C to 150°C

DescriptionThe QuadPHY interface device is a single-chip, multi-PHY (four 10BASE-T devices), high-performance solution for designers of 10BASE-T networking systems. The highly integrated TNETE2004 includes a user-programmable SNI signal for each PHY. Each PHY interface on the device provides Manchester encoding/decoding of data via unshielded twisted-pair (UTP) balanced cable through simple isolation transformers requiring no external filtering. Additional TNETE2004 features are smart squelch, jabber detection, auto-polarity correction, transmission wave shaping, and anti-alias filtering capabilities. Each PHY interface on the TNETE2004 is individually addressable within the TNETE2004 via the MDIO.

It provides PHY-interface functions for up to four 10BASE-T half- or full-duplex ports as shown in Figure 1. The TNETE2004 contains four independent 10BASE-T transceivers in a single chip. Each transceiver is compliant with IEEE Std 802.3, Section 14, and a compliant management serial-interface port provides information for network management. A typical application with external components is shown in Figure 2.

TNETE2004 Data Sheet

TNETE2004 Data Sheet