Features: ` Single-Chip Scheduler for Scheduling

Available Bit Rate (ABR) Connections

` Used With the TNETA1575 to Provide a

Complete Solution for Segmentation and Reassembly of Data on ABR Connections

as Specified in the Asynchronous Transfer

Mode (ATM) Forum's Traffic Management

4.0 Document (TM4.0) and ITU-TI.371

` Supports Scheduling of Variable-Bit-Rate

Non-Real Time (VBR-nrt) Using

Host-Programmable Peak Cell Rate (PCR),Sustained Cell Rate (SCR), and Maximum Burst Size (MBS)

` On-Chip Self-Sorting FIFO-Based

Scheduler Used to Schedule the Transmission of Cells for All Connections

` Simultaneously Supports Both Virtual Path

(VP) and Virtual Channel (VC) Level ABR Traffic Management

` Provides Scheduling for up to 2047 ABR

Connections Required for Large-Scale LAN Emulation Installations

` End-System Behavior as Defined in TM4.0,Providing a High-Performance and Flexible Solution to Track Future Standards

` On-Chip Instruction RAMs Hold the Microcode for the Source and Destination Processors, Providing Fast Execution of Code on Chip

` Configuration Support for all Primary and Optional TM4.0 Parameters, Providing

Maximum Implementation Flexibility

` Supports TM4.0-Defined Resource

Management (RM)-Cell Formats and Provides the RM-Cell Payload and

Information on How to Configure the RM-Cell Header to the Segementation and Reassembly (SAR) Device

` Supports Out-of-Rate Forward and Backward RM-Cell Generation to Prevent

Deadlock Situations When the Rates of Sources and Destinations Are Driven to or Below a Minimum Cell Rate of 10 Cells Per Second

` Processes Received RM Cells, Maintaining

Parameters and Variables in Accordance With TM4.0

` Hardware Assistance Is Provided for 1/ACR

Calculations That Support Scheduling

Operations to Maximize Performance

` Hardware Assistance Is Provided for 15-bit

Floating-Point To/From Integer

Conversions to Maximize Performance

` UTOPIA Revision 2.01-Compliant Receive

(Observe-Only) Cell Interface

` nternal 8-Cell Receive FIFO

` Receive-Cell Interface Can Be Programmed to Operate as Either a Physical (PHY-Layer)

Interface or as a SAR/Switch (ATM-Layer) Interface.

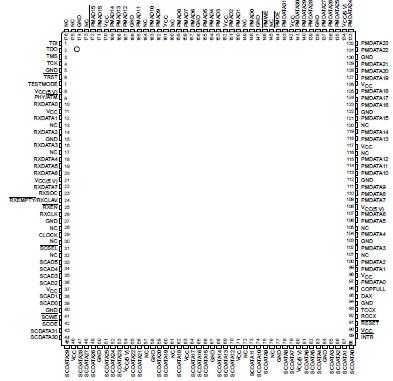

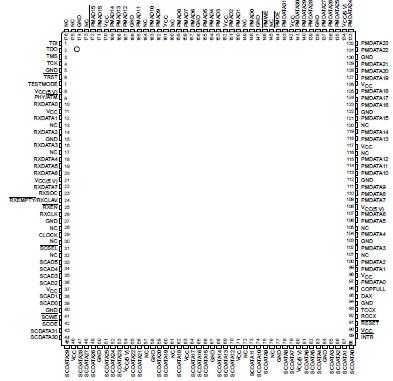

` Supports Boundary Scan Through a Five-Wire JTAG Interface in Accordance With IEEE Std 1149.1-1990 (Includes IEEE Std 1149.1a-1993) IEEE Standard Test- Access-Port and Boundary-Scan ArchitecturePinout Specifications

SpecificationsSupply voltage range, VCC (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 4 V

Supply voltage range, VCC(5 V) (see Note 1) . . . . . . . . . . . . . . . . . . . . . . 0.5 V to 5.5 V

Input voltage range, standard TTL, VI . . . . . . . . . . . . . . . . . . . . . . 0.5 V to VCC + 0.5 V

Input voltage range, 5-V tolerant TTL, VI . . . . . . . . . . . . . . . . . . . . . . . .. VCC(5V) + 0.5 V

Output voltage range, standard TTL, VO . . . . . . . . . . . . . . . . . . . . 0.5 V to VCC + 0.5 V

Output voltage range, 5-V tolerant TTL, VO . . . . . . . . . . . . . . . . . .. . . 5 V to VCC + 0.5 V

Input clamp current, TTL, IIK (VI < 0 or VI > VCC) (see Note 2) . . . . . . .. . . . ... . . ±20 mA

Output clamp current, IOK (VO < 0 or VO > VCC) (see Note 3) . . . . . . . . . . . . . . . ±20 mA

Operating free-air temperature range, TA . . . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to 70°C

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65°C to 150°C

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values are with respect to the GND terminals.

2. Applies for external input and bidirectional buffers without hysteresis. VI > VCC does not apply to fail-safe terminals. Use VI > VCC(5 V) for 5-V tolerant terminals.

3. Applies for external output and bidirectional buffers. VO > VCC does not apply to fail-safe terminals. Use VO > VCC(5 V) for 5-V tolerant terminals.

DescriptionThe TNETA1585 is an asynchronous transfer mode (ATM) programmable traffic management scheduler device that is used with a segmentation and reassembly (SAR) device to provide a flexible, high-performance solution for the available bit rate (ABR) service category. Its programmability enables it to support other special modes including variable-bit-rate non-real-time (VBR-nrt) service category and virtual path (VP) level ABR in addition to and simultaneously with ABR. Combining the TNETA1585 with the TNETA1575 provides a high-performance solution for classical LAN to ATM backbone applications including high-performance networking hubs.

This data sheet provides information on the device hardware specifications that includes device interfaces, timing diagrams, electrical characteristics, terminal and package information, and an overview of device operation. All information on the TNETA1585 data structures, configuration, and features is provided in the TNETA1585 Programmer's Reference Guide, literature number SDNU016.

TNETA1585 Data Sheet

TNETA1585 Data Sheet