Features: 10-Bit Resolution 20 MSPS Sampling

Analog-to-Digital Converter (ADC)

Power Dissipation . . . 107 mW Typ

5-V Single Supply Operation

Differential Nonlinearity . . . ±0.5 LSB Typ

No Missing Codes

Power Down (Standby) Mode

Three State Outputs

Digital I/Os Compatible With 5-V or 3.3-V

Logic

Adjustable Reference Input

Small Outline Package (SOIC), Super Small

Outline Package (SSOP), or Thin Small

Outline Package (TSOP)

Pin Compatible With the Analog

Devices AD876ApplicationCommunications

Multimedia

Digital Video Systems

High-Speed DSP Front-End ...TMS320C6x

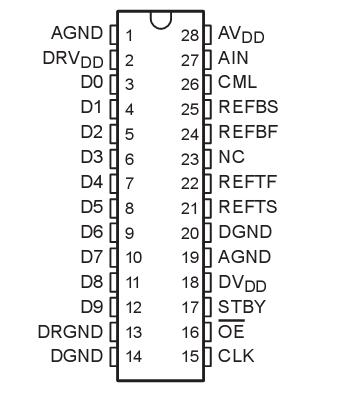

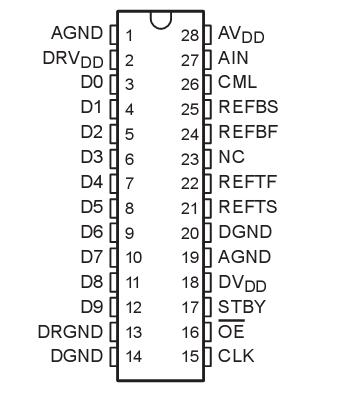

Pinout SpecificationsSupply voltage, AVDD to AGND, DV DD to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.3 V to 6.5 V

SpecificationsSupply voltage, AVDD to AGND, DV DD to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.3 V to 6.5 V

Reference voltage input range to AGND, V I(REFTF),

V I(REFBF), V I(REFBS), VI(REFTS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 0.3 V to AV + 0.3 VDD

Analog input voltage range to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ... . . . . 0.3 V to AV DD + 0.3 V

Digital input voltage range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.3 V to DVDD + 0.3 V

Digital output voltage range applied from external source . . . . . . . . . . . . . . . . . . . . . . . ... . . . . . 0.5 V to DVDD

Operating virtual junction temperature range, TJ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-55 to 150

Operating free-air temperature range, TA : TLC876C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 to 70

TLC876I . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .... -45 °C to 85

TLC876M . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .... -55°C to 125

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . -65 to 150

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . 260°CDescriptionThe TLC876C is a CMOS, low-power, 10-bit, 20 MSPS analog-to-digital converter (ADC). The speed, resolution, and single-supply operation are suited for applications in video, multimedia, imaging, high-speed acquisition, and communications. The low-power and single-supply operation satisfy requirements for high-speed portable applications. The speed and resolution ideally suit charge-coupled device (CCD) input systems such as color scanners, digital copiers, electronic still cameras, and camcorders. A multistage pipelined architecture with output error correction logic provides for no missing codes over the full operating temperature range. Force and sense connections to the reference inputs provide a more accurate internal reference voltage to the reference resistor string.

A standby mode of operation reduces the power to typically 15 mW. The TLC876C to either 5-V or 3.3-V logic and the digital output terminals can be placed in a high-impedance state. The format of the output data is straight binary coding.

A pipelined multistaged architecture achieves a high sample rate with low power consumption. The TLC876C distributes the conversion over several smaller ADC sub-blocks, refining the conversion with progressively higher accuracy as the device passes the results from stage to stage. This distributed conversion requires a small fraction of the 1023 comparators used in a traditional flash ADC. A sample-and-hold amplifier (SHA) within each of the stages permits the first stage to operate on a new input sample while the second through the fifth stages operate on the four preceding samples.

TLC876C Data Sheet

TLC876C Data Sheet