Features: ` Single-chip 5 V mixer/oscillator and low phase noise PLL synthesizer for TV and VCR tuners, dedicated to hybrid (digital and analog) as well as pure digital applications (DVB-T)

` Five possible step frequencies to cope with different digital terrestrial TV and analog TV standards

` Eight charge pump currents between 40 and 600 mA to reach the optimum phase noise performance over the bands

` Automatic Loop Bandwidth Control (ALBC) sets the optimum phase noise performance for DVB-T channels

` I2C-bus protocol compatible with 2.5, 3.3 and 5 V microcontrollers:

Address + 5 data bytes transmission (I2C-bus write mode)

Address + 1 status byte (I2C-bus read mode)

Four independent I2C-bus addresses

` Five PMOS open-drain ports with 15 mA source capability for band switching and general purpose; one of these ports is combined with a 5-step ADC

` Wide band AGC detector for internal tuner AGC:

Six programmable take-over points

Two programmable time constants

AGC flag

` In-lock flag

` Crystal frequency output buffer

` 33 V tuning voltage output

` Fractional-N programmable divider

` Balanced mixers with a common emitter input for the low band and for the mid band (each single input)

` Balanced mixer with a common base input for the high band (balanced input)

` 2-pin asymmetrical oscillator for the low band

` 2-pin symmetrical oscillator for the mid band

` 4-pin symmetrical oscillator for the high band

` Switched concept IF amplifier with both asymmetrical and symmetrical outputs to drive low impedance or SAW filters i.e. 500 W//40 pF.

Application· Digital and analog terrestrial tuners (OFDM, PAL, etc.)

· Cable tuners (QAM)

· Digital TV sets

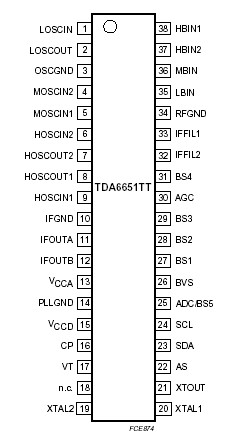

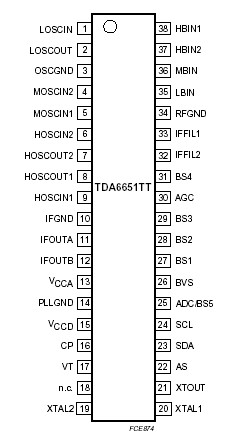

· Digital set-top boxes.Pinout

Specifications

| SYMBOL |

PARAMETER |

CONDITIONS |

MIN. |

MAX. |

UNIT |

VCCA,

VCCD |

supply voltage |

|

-0.3 |

+6 |

V |

| VVT |

tuning voltage output |

|

-0.3 |

+35 |

V |

| VSDA |

serial data input and output voltage |

|

-0.3 |

+6 |

V |

| ISDA |

serial data output current |

during acknowledge |

0 |

10 |

mA |

| VSCL |

serial clock input voltage |

|

-0.3 |

|

V |

| VAS |

address selection input voltage |

|

-0.3 |

|

V |

| Vn |

voltage on all other inputs, outputs and

combined inputs and outputs, except

GNDs |

4.5 V< VCC < 5.5 V |

-0.3 |

VCC + 0.3 |

V |

| IBSn |

PMOS port output current |

corresponding port on;

open-drain |

-20 |

0 |

mA |

| IBS(tot) |

sum of all PMOS port output currents |

open-drain |

-50 |

0 |

mA |

| tsc(max) |

maximum short-circuit time |

each pin to VCC or to GND |

- |

10 |

s |

| Tstg |

storage temperature |

|

-40 |

+150 |

|

| Tamb |

ambient temperature |

|

-20 |

Tamb(max)

(2) |

|

| Tj |

junction temperature |

|

- |

+150 |

|

DescriptionThe TDA6650TT; TDA6651TT is a programmable 3-band mixer/oscillator and low phase noise PLL synthesizer intended for pure 3-band tuner concepts applied to hybrid (digital and analog) terrestrial and cable TV reception.

The TDA6650TT; TDA6651TT include three double balanced mixers for low, mid and high bands, three oscillators for the corresponding bands, a switchable IF amplifier, a wide band AGC detector and a low noise PLL synthesizer. The frequencies of the three bands are shown in Table 1. Two pins of TDA6650TT; TDA6651TT are available between the mixer output and the IF amplifier input to enable IF filtering for improved signal handling and to improve the adjacent channel rejection.

The IF amplifier TDA6650TT; TDA6651TT is switchable in order to drive both symmetrical and asymmetrical outputs. When it is used as an asymmetrical amplifier, the IFOUTB pin needs to be connected to the supply voltage VCCA.

Five open-drain PMOS ports of TDA6650TT; TDA6651TT are included on the IC. Two of them, BS1 and BS2, are also dedicated to the selection of the low, mid and high bands. PMOS port BS5 pin is shared with the ADC.

The AGC detector TDA6650TT; TDA6651TT provides a control that can be used in a tuner to set the gain of the RF stage. Six AGC take-over points are available by software. Two programmable AGC time constants are available for search tuning and normal tuner operation.

The local oscillator signal of TDA6650TT; TDA6651TT is fed to the fractional-N divider. The divided frequency is compared to the comparison frequency into the fast phase detector which drives the charge pump. The loop amplifier is also on-chip, including the high-voltage transistor to drive directly the 33 V tuning voltage without the need to add an external transistor. The comparison frequency is obtained from an on-chip crystal oscillator. The crystal frequency TDA6650TT; TDA6651TT can be output to the XTOUT pin to drive the clock input of a digital demodulation IC.

Control data is entered via the I2C-bus; six serial bytes are required to address the TDA6650TT; TDA6651TT, select the local oscillator (LO) frequency, select the step frequency, program the output ports and set the charge pump current or select the ALBC mode, enable or disable the crystal output buffer, select the AGC take-over point and time constant and/or select a specific test mode. A status byte concerning the AGC level detector and the ADC voltage of TDA6650TT; TDA6651TT can be read out on the SDA line during a read operation. During a read operation, the loop 'in-lock' flag, the Power-on reset flag and the automatic loop bandwidth control flag are read.

The TDA6650TT; TDA6651TT have 4 programmable addresses. Each address can be selected by applying a specific voltage to pin AS, enabling the use of multiple TDA6650TT; TDA6651TT in the same system. The I2C-bus is fast mode compatible, except for the timing as described in the functional description and is compatible with 5, 3.3 and 2.5 V microcontrollers depending on the voltage applied to pin BVS.

TDA6651TT Data Sheet

TDA6651TT Data Sheet