Features: · Single chip 5 V mixer/oscillator-PLL synthesizer for

hyperband tuners

· I2C-bus protocol

· 3 PNP band switch buffers (25 mA)

· 33 V tuning voltage output

· In-lock detector

· 5-level Analog-to-Digital Converter (ADC)

· 15-bit programmable divider

· Programmable reference divider ratio

(512, 640 or 1024)

· Programmable charge pump current

· Balanced mixer with a common emitter input for VHF

(single input)

· Balanced mixer with a common base input for UHF

(double input)

· 4-pin common emitter oscillator for VHF

· 4-pin common emitter oscillator for UHF

· IF amplifier with a low output impedance to drive a SAW

filter directly (»2 kW load)

· Low power, low radiation, small sizeApplication· Hyperband tuners for Europe using a 2-band

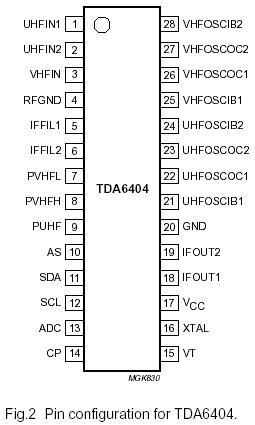

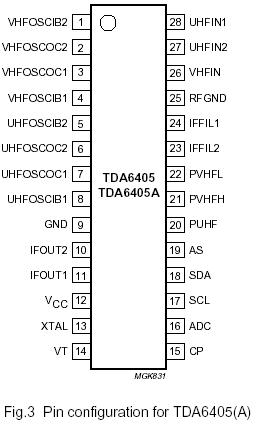

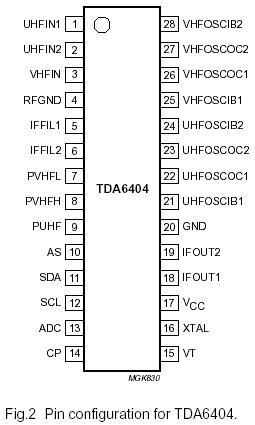

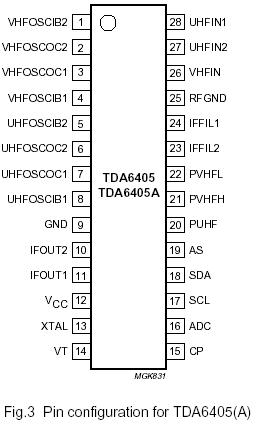

mixer/oscillator in a switched concept.Pinout

Description

DescriptionThe TDA6404, TDA6405 and TDA6405A are programmable 2-band mixer/oscillator-PLL synthesizers intended for VHF/UHF and hyperband tuners (see Fig.1).

The TDA6404, TDA6405 and TDA6405A include two double balanced mixers and two oscillators for the VHF and UHF band, an IF amplifier and a PLL synthesizer. With proper oscillator application and by using a switchable inductor to split the VHF band into two sub-bands (the full VHF/UHF and hyperband) the TV bands can be covered.

Two pins of TDA6404, TDA6405 and TDA6405A are available between the mixer output and the IF amplifier input to enable IF filtering for improved signal handling. Three PNP ports of TDA6404, TDA6405 and TDA6405A are provided for band switching. Band selection is made according to the band switch bits VHFL, VHFH and UHF.

The PLL synthesizer consists of a divide-by-eight prescaler, a 15-bit programmable divider, a 4 MHz crystal oscillator and its programmable reference divider and a phase comparator combined with a charge pump which drives the tuning amplifier, including 33 V output.

Depending on the reference divider ratio (512, 640 or 1024), the phase comparator operates at 7.8125 kHz, 6.25 kHz or 3.90625 kHz.

The TDA6404, TDA6405 and TDA6405A are controlled according to the I2C-bus format. The in-lock detector bit FL is set to logic 1 when the loop is locked and is read on the SDA line (status byte) during a read operation. The ADC input of TDA6404, TDA6405 and TDA6405A is available for digital Automatic Frequency Control (AFC). The ADC code is read during a read operation on the I2C-bus (see Table 9). In test mode, pin ADC is used as a test output for fREF and 1¤2fDIV.

TDA6405 Data Sheet

TDA6405 Data Sheet