Features: · 2 and 8 kbytes Coded Orthogonal Frequency Division Multiplexer (COFDM) demodulator (fully DVB-T compliant: ETSI 300-744)

· All modes supported, including hierarchical modes

· Fully automatic transmission parameters detection (including Fast Fourier Transformer (FFT) size and guard interval)

· Digital Signal Processor (DSP) based synchronization (software can be upgraded on the fly)

· No extra-host software required

· On-chip 10-bit Analog-to-Digital Converter (ADC)

· 2nd or 1st IF variable analog input

· Only fundamental crystal oscillator required (4 MHz typical ±100 ppm)

· 6, 7 and 8 MHz channels with the same crystal

· Pulse killer algorithm to protect against impulse noise

· Digital frequency correction (±90 kHz)

· Frequency offset (±1/6 MHz) automatic estimator to speed-up the scan

· RF tuner input power measurement

· Parallel or serial transport stream interface

· BER measurement (before and after Viterbi decoder)

· Signal-to noise ratio estimation

· Constellation, CSI and channel frequency response outputs

· TPS bits I2C-bus readable (including spare ones)

· Controllable dedicated I2C-bus for the tuner (5 V tolerant)

· 3 low frequency spare DACs and 2 spare inputs

· CMOS 0.2 mm technology.Application· DVB-T fully compatible

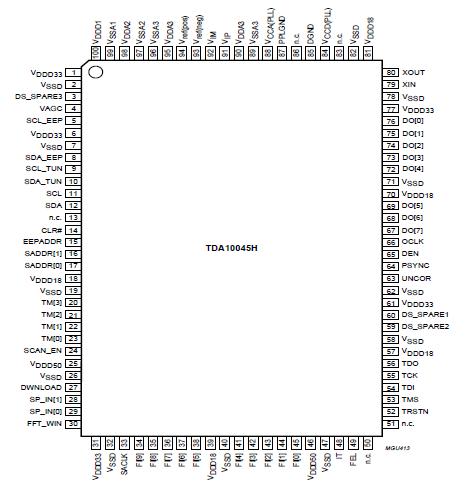

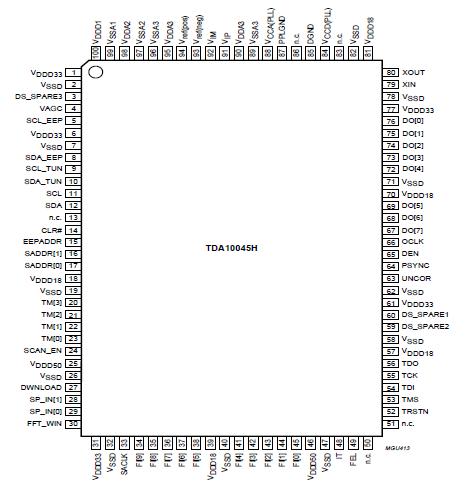

· Digital data transmission using COFDM modulation.Pinout SpecificationsIn accordance with the Absolute Maximum Rate System (IEC 60134); note 1.

SpecificationsIn accordance with the Absolute Maximum Rate System (IEC 60134); note 1.

| SYMBOL |

PARAMETER |

MIN. |

MAX. |

UNIT |

| VDDD18 |

digital supply voltage for the core |

-0.5 |

+2.1 |

V |

| VDDD33 |

digital supply voltage for the pads |

-0.5 |

+3.8 |

V |

| VI |

DC input voltage |

-0.5 |

+5.5 |

V |

| II |

DC input current |

- |

±20 |

mA |

| Tlead |

lead temperature |

- |

300 |

°C |

| Tstg |

storage temperature |

-65 |

+150 |

°C |

| Tj |

junction temperature |

- |

150 |

°C |

| Tamb |

ambient temperature |

0 |

70 |

°C |

Note

1. Stresses above the Absolute Maximum Ratings may cause permanent damage to the device. Exposure to AbsoluteMaximum Ratings conditions for extended periods may affect device reliability.

DescriptionThe TDA10045H is a single-chip channel receiver for 2 and 8 kbytes COFDM modulated signals based on the ETSI specification (ETSI 300-744). The device interfaces directly to an IF signal, which could be either 1st or 2nd IF and integrates a 10-bit Analog-to-Digital Converter (ADC), a Numerically Controlled Oscillator (NCO) and a Phase-Locked Loop (PLL), simplifying external logic requirements and limiting system costs.

The TDA10045H performs all the COFDM demodulation tasks from IF signal to the MPEG-2 transport stream. An internal DSP core manages the synchronization and the control of the demodulation process, and implements specially developed software for robustness against co-channel and adjacent channel interference, to deal with Single Frequency Network (SFN) echo situations, and to assist in a very fast scan of the bandwidth. After baseband conversion and FFT demodulation, the channel frequency response is estimated, which is based on the scattered pilots, and filtered in both time and frequency domains. This estimation is used as a correction on the signal, carrier by carrier. A common phase error and estimator is used to deal with the tuner phase noise. The Forward Error Correction TDA10045H (FEC) decoder is automatically synchronized by the frame synchronization algorithm that uses the TPS information included in the modulation. An embedded 'pulse killer' algorithm enables the bad effects of short and strong impulsive noise interference that could be caused by electrical domestic devices and/or car traffic to be greatly reduced.

This device is controlled via an I2C-bus (master). The chip provides 2 switchable I2C-buses derived from the master: a tuner I2C-bus to be disconnected from the I2C-bus master when not necessary and an EEPROM I2C-bus.

The DSP software code can be fed to the chip via the master I2C-bus or via the dedicated EEPROM I2C-bus. Designed in 0.2 mm CMOS technology and housed in a 100 pin QFP package, the TDA10045H operates over the commercial temperature range.

TDA10045H Data Sheet

TDA10045H Data Sheet