Features: ` 3.3 V operation

` Per-channel programmable gains, equalization, termination impedance, and hybrid balance

` Programmable m-law, linear, or A-law modes:

- Up to 256 time slots per frame

- Supports PCM data rates of 512 kbits/s to 16.384 Mbits/s

- Double-clock mode timing compatible with ISDN standard interfaces

` Fully programmable time-slot assignment with bit offset

` Analog and digital loopback test modes

` Serial microprocessor interface:

- Normal and byte-by-byte control modes

- Fast scan mode

` Six bidirectional control leads per channel, for SLIC and line card function control

` Differential analog output:

- Mates directly to SLICs, eliminating external components

` Sigma-delta converters with dither noise reduction

` Quad design to minimize package count on dense line card applications

` Meets or exceeds ITU-T G.711-G.712 and relevant Telcordia TechnologiesTM requirementsApplicationThe following reference circuit shows a complete schematic for interfacing to the Agere L9215G SLIC. All ac

parameters are programmed by the T8538B. Note that this implementation differentiates itself in that no external

components are required in the ac interface to provide a dc termination impedance or for stability. For illustration

purposes, 0.5 Vrms PPM injection was assumed in this example and no meter pulse rejection is used. Also, this

example illustrates the device using programmable overhead and current limit.Pinout Specifications

Specifications

|

Parameter |

Symbol |

Min |

Max |

Unit |

| Storage Temperature Range |

Tstg |

55 |

150 |

°C |

| Power Supply Voltage (all leads designated power) |

VDDX |

- |

VDDX+0.5 |

V |

| Negative Voltage on Any Lead with Respect to Ground |

VSS |

-0.25 |

- |

V |

Thermal Resistance, Junction to Ambient:

64-Pin TQFP1

|

RQJA |

- |

40 |

°C/W |

| 100-Pin TQFP1 |

RQJA |

- |

30 |

°C/W |

| Package Power Dissipation |

PD |

- |

1 |

W |

| SLIC Control Interface Latches, Current per Device |

IL |

- |

160 |

mA |

DescriptionThe T8538B consists of four independent channels of codec and digital signal processing functions on one chip. In addition to the classic A-to-D and D-to-A conversion, each channel provides termination impedance synthesis and a hybrid balance network.

The T8538B is controlled by a serial microprocessor interface, and a series of bidirectional I/O leads are provided so that this control mechanism can be utilized to operate the battery feed device, ringing voltage switches, etc. Common data and clock paths can be shared over any number of devices. All the filter coefficients, signal processing, SLIC, and test features are accessible through this interface. This serial interface can be operated at speeds up to 16 Mbits/s.

The choice of a PCM bus is also programmable, with any channel capable of being assigned to any time slot. The PCM bus can be operated at speeds up to 16.384 Mbits/s, allowing for a maximum of 256 time slots. Separate transmit and receive interfaces are available for 4-wire bus designs, or they can be strapped together for a 2-wire PCM bus.

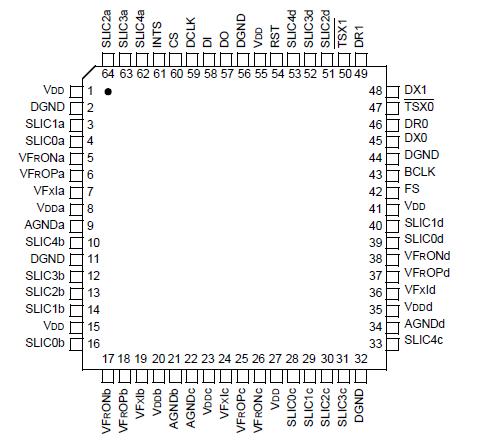

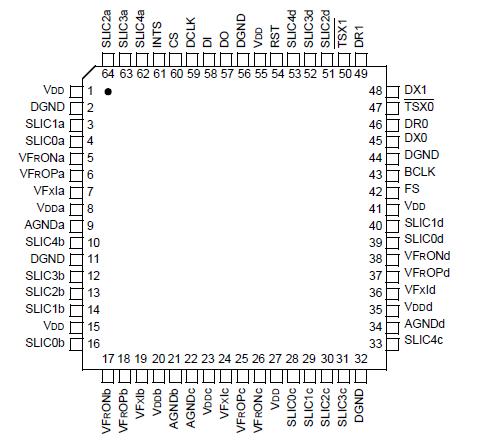

The device is available in two packages.

The T8538B 64-pin TQFP features five data latches per channel and the 100-pin TQFP features six data latches per channel.

Both devices are pin-compatible with the T8536B 5 V quad programmable codecs.

T8538B Data Sheet

T8538B Data Sheet