Features: `700MHz min. count frequency

`Extended 100E VEE range of 4.2V to 5.5V

`1000ps CLK to Q, TC

`Internal, gated TC feedback

`8 bits wide

`Fully synchronous counting and TC generation

` Asynchronous Master Reset

`Fully compatible with industry standard 10KH, 100K I/O levels

`Internal 75K input pulldown resistors

`Fully compatible with Motorola MC10E/100E016

`Available in 28-pin PLCC packageApplicationFor applications which call for larger than 8-bit counters, multiple E016s can be tied together to achieve very wide bit width counters. The active low terminal count (TC) output and count enable input (CE) greatly facilitate the cascading of E016 devices. Two E016s can be cascaded without the need for external gating; however, for counters wider than 16 bits, external OR gates are necessary for cascade implementations.

Figure 1, below, pictorially illustrates the cascading of 4 E016s to build a 32-bit high frequency counter. Note the E101 gates used to OR the terminal count outputs of the lower order E016s to control the counting operation of the higher order bits. When the terminal count of the preceding device (or devices) goes low (the counter reaches an all 1s state), the more significant E016 is set in its count mode and will count one binary digit upon the next positive clock transition. In addition, the preceding devices will also count one bit, thus sending their terminal count outputs back to a high state, disabling the count operation of the more significant counters and placing them back into hold modes. Therefore, for an E016 in the chain to count all of the lower order terminal count outputs, it must be in the low state. The bit width of the counter can be increased or decreased by simply adding or subtracting E016 devices from Figure 1 and maintaining the logic patternillustrated in the same figure.

The maximum frequency of operation for the cascaded counter chain is set by the propagation delay of the TC output and the necessary set-up time of the CE input and the propagation delay through the OR gate controlling it (for 16-bit counters the limitation is only the TC propagation delay and the CE set-up time). Figure 1 shows E101 gates used to control the count enable inputs; however, if the frequency of operation is lower, a slower ECL OR gate can be used. Using the worst case guarantees for these parameters from the ECLinPS data book, the maximum count frequency for a greater than 16-bit counter is 475MHz and that for a 16-bit counter is 625MHz. Note that this assumes the trace delay between the TC outputs and the CE inputs are negligible. If this is not the case, estimates of these delays need to be added to the calculations.

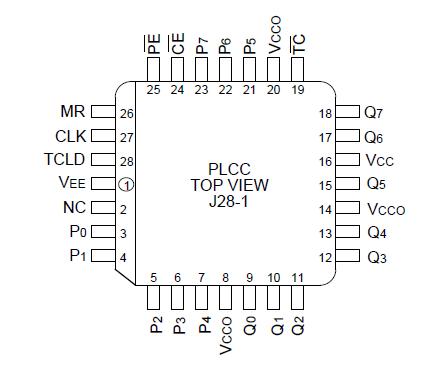

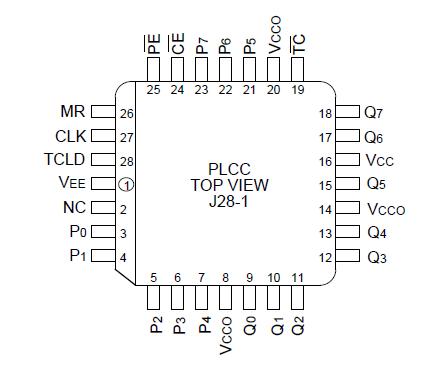

Pinout Description

DescriptionThe SY100E016 is high-speed synchronous, presettable and cascadable 8-bit binary counters designed for use in new, high-performance ECL systems. Architecture and operation are the same as the Motorola MC10H016 in the MECL 10KH family, extended to 8 bits, as shown in the logic diagram.

The SY100E016 feature internal feedback of TC, gated by the TCLD (terminal count load) pin. When TCLD is LOW, the TC feedback is disabled and counting proceeds continuously, with TC going LOW to indicate an all-HlGH state. When TCLD is HIGH, theTC feedback causes the counter to automatically reload upon TC = LOW, thus functioning as a programmable counter.

SY100E016 Data Sheet

SY100E016 Data Sheet