Features: `High Performance 16-bit CPU with 4-Stage Pipeline

`100 ns Instruction Cycle Time at 20-MHz CPU Clock

`500 ns Multiplication (16 * 16 bits), 1 s Division (32 / 16 bit)

`Enhanced Boolean Bit Manipulation Facilities

`Additional Instructions to Support HLL and Operating Systems

`Register-Based Design with Multiple Variable Register Banks

`Single-Cycle Context Switching Support

`Up to 16 MBytes Linear Address Space for Code and Data

`2 KBytes On-Chip RAM

`4 KBytes On-Chip ROM (RM types only)

`Programmable External Bus Characteristics for Different Address Ranges

`8-Bit or 16-Bit External Data Bus

`Multiplexed or Demultiplexed External Address/Data Buses

`Five Programmable Chip-Select Signals

`Hold- and Hold-Acknowledge Bus Arbitration Support

`1024 Bytes On-Chip Special Function Register Area

`Idle and Power Down Modes

`8-Channel Interrupt-Driven Single-Cycle Data Transfer Facilities via Peripheral Event Controller (PEC)

`Two Multi-Functional General Purpose Timer Units with 5 Timers

`Two Serial Channels (Synchronous/Asynchronous and High-Speed-Synchronous)

`Programmable Watchdog Timer

`Up to 77 General Purpose I/O Lines

`Supported by a Wealth of Development Tools like C-Compilers, Macro-Assembler Packages,Emulators, Evaluation Boards, HLL-Debuggers, Simulators, Logic Analyzer Disassemblers,Programming Boards

`On-Chip Bootstrap Loader

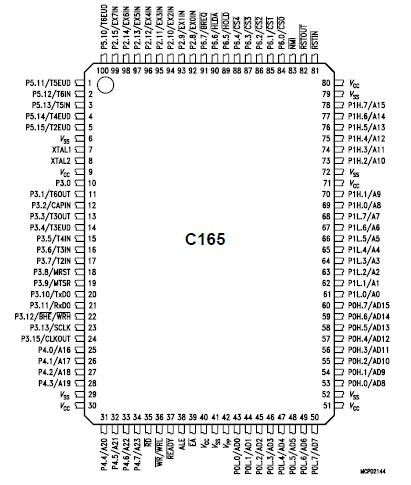

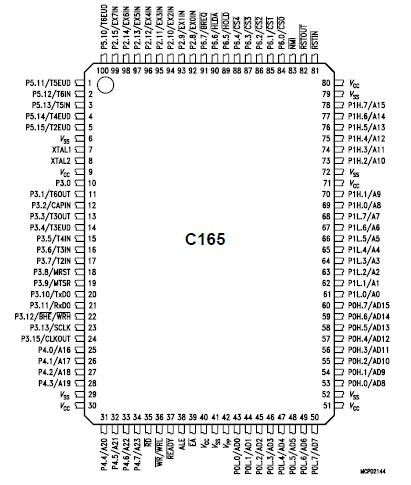

`100-Pin MQFP Package (EIAJ)

`100-Pin TQFP Package (Thin QFP)

Pinout Specifications

SpecificationsAmbient temperature under bias (TA):

SAB-C165-LM, SAB-C165-RM, SAB-C165-LF, SAB-C165-RF ... 0 to + 70 °C

SAF-C165-LM................................................................... 40 to + 85 °C

Storage temperature (TST) ........................................... 65 to + 150 °C

Voltage on VCC pins with respect to ground (VSS)............ 0.5 to + 6.5 V

Voltage on any pin with respect to ground (VSS) ....... 0.5 to VCC + 0.5 V

Input current on any pin during overload condition.......... 10 to + 10 mA

Absolute sum of all input currents during overload condition ........|100 mA|

Power dissipation.............................................................................. 1.5 W

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During overload conditions (VIN > VCC or VIN < VSS) the

voltage on pins with respect to ground (VSS) must not exceed the values defined by the Absolute Maximum Ratings.

DescriptionThe architecture of the C165 combines advantages of both RISC and CISC processors and of advanced peripheral subsystems in a very well-balanced way. The following block diagram gives an overview of the different on-chip components and of the advanced, high bandwidth internal bus structure of the C165.

SAF-C165-LM Data Sheet

SAF-C165-LM Data Sheet