Features: • Single-chip Peripheral Component Interface (PCI) Bus Local ATM Network Interface using SONET/SDH framing at 155.52 or 51.84 Mbit/s and ATM Adaptation Layer 5 (AAL-5).

• Implements the ATM Physical Layer according to the ATM Forum User Network Interface Specification and ITU-TS Recommendation I.432, and the ATM Adaptation Layer Type 5 (AAL-5) for Broadband ISDN according to ITU-TS Recommendation I.363.

• Provides a direct interface to multimode or single mode optical modules or twisted

pair wiring (UTP-5) modules, with on-chip clock recovery and clock synthesis.

• Directly supports a 32-bit PCI bus interface for configuration, monitoring and transfer of packet data, with an on-chip DMA controller with scatter/gather capabilities. Other 32 bit system buses can be accommodated using external glue logic.

• Provides an on-chip 96 cell receive buffer to accommodate up to 270 µs of PCI Bus latency.

• Provides a optional microprocessor port with master and slave capabilities.

• Provides a SCI-PHY and Utopia compliant interface for connection to external PHY layer devices.

• Supports simultaneous segmentation and reassembly of 128 virtual circuits (VCs) in both transmit and receive directions.

• Provides leaky bucket peak cell rate enforcement using 8 programmable peak queues coupled with sub peak control on a per VC basis; provides sustainable cell rate enforcement using the programmable peak cell rate queues and per VC token bucket averaging; and provides aggregate peak cell rate enforcement.

• Provides a generic constant bit-rate (CBR) port.

• Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board test purposes.

• Low power, 0.6 micron, +5 Volt CMOS technology.

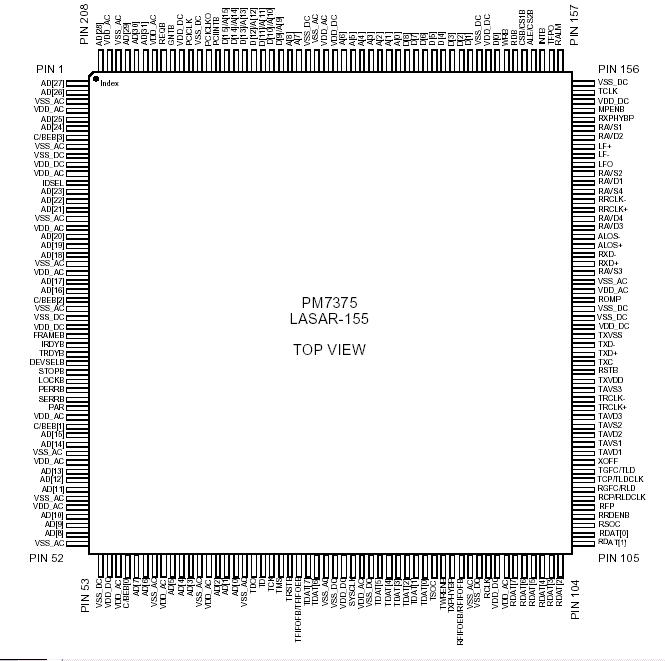

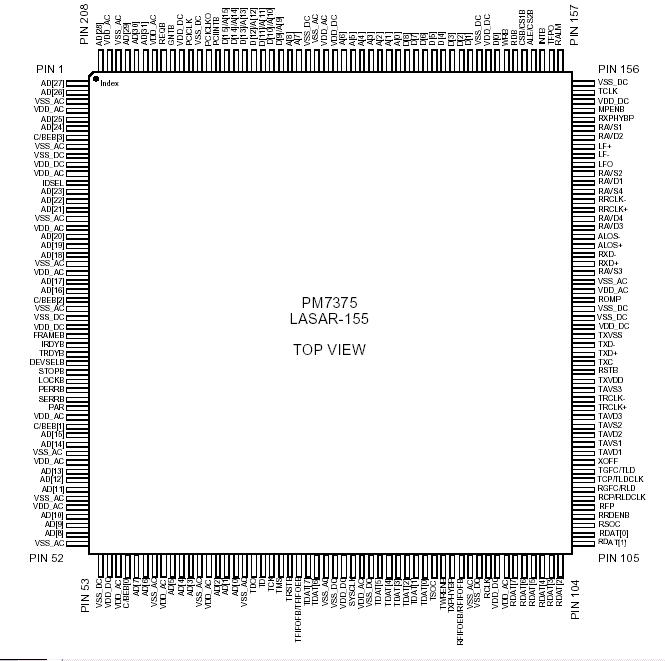

• 208 copper slugged plastic quad flat pack (PQFP) package.

Application• ATM Workstations and Servers

• ATM Bridges, Switches and Hubs

• Multimedia TerminalsPinout SpecificationsCase Temperature under Bias . . . . . . . . . . . . . . . . . . . . 0°C to +70°C

SpecificationsCase Temperature under Bias . . . . . . . . . . . . . . . . . . . . 0°C to +70°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . .-40°C to +125°C

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . -0.5V to +6.0V

Voltage on Any Pin . . . . . . . . . . . . . . . . . . . . . . . . . .-0.5V to VDD+0.5V

Static Discharge Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . .±1000 V

Latch-Up Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .±100 mA

DC Input Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .±20 mA

Lead Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +300°C

Absolute Maximum Junction Temperature . . . . . . . . . . . . .. . . .+150°CDescriptionThe PM7375 LASAR-155 Local ATM Segmentation and Reassembly & Physical Layer device is a monolithic integrated circuit that implements SONET/SDH transmission convergence, ATM cell mapping, ATM Adaptation Layer, and PCI Bus memory management functions for a 155.52 or 51.84 Mbit/s ATM User Network Interface.

The LASAR-155 receives SONET/SDH frames via a bit serial interface, recovers clock and data, and processes section, line, and path overheads. PM7375 performs framing (A1, A2), descrambling, detects alarm conditions, and monitors section, line, and path bit interleaved parity (B1, B2, B3), accumulating error counts at each level for performance monitoring purposes. Line and path far end block error indications (Z2, G1) are also accumulated. The LASAR-155 PM7375 interprets the received payload pointers (H1, H2) and extracts the synchronous payload envelope which carries the received ATM cell payload.

The LASAR-155 frames to the ATM payload using cell delineation. Payload descrambling, HEC single bit error correction, cell filtering based on HEC errors and idle/unassigned cell filtering is provided. The Generic Flow Control (GFC) field is extracted from all received cell headers of PM7375 and serialized out a dedicated port. Counts of received ATM cell headers that are in error and uncorrectable, cell headers that are errored and correctable and all passed cells are accumulated independently for performance monitoring purposes.

The LASAR-155 supports the simultaneous reassembly and Common Part Convergence Sublayer (CPCS) processing for 128 open Virtual Circuits (VCs). All receive VC parameters are stored locally in the LASAR-155 device to reduce overhead traffic on the PCI Host bus. The LASAR-155 takes all received error free cells and passes or blocks the cell based on an open VC. Passed cells of PM7375 are treated as management, control or user cells. Management and control cell payloads are optionally checked with a CRC-10 polynomial and are optionally DMA'd to receive ready queues in packet memory.

User cells are associated with an open VC and DMA'd to reassembly queues in packet memory. Once a packet is reassembled and verified using a CRC-32 polynomial, the entire packet is linked into a receive ready queue. The LASAR-155 alerts the PCI Host that there are reassembled packets or cells in a receive ready queue by asserting an interrupt on the PCI bus.

All transmit VC parameters of PM7375 are stored in an internal transmit parameter table to reduce overhead traffic on the PCI bus. After a PCI Host sets up a connection using the transmit parameter table, the PCI Host can provide packets to transmit using a high or low priority ready queue. The LASAR-155 automatically appends the AAL-5 trailer, segments the packet of PM7375 and subjects the cells to either peak cell rate or sustainable cell rate enforcement.

The LASAR-155 generates most of a cell's header using the transmit parametertable. The generic flow control (GFC)PM7375 bits may optionally be inserted using a dedicated serial port. The header error code (HEC) is automatically calculated and inserted. The cell payload is optionally scrambled. Generated transmit cells are automatically inserted into a STS-3c (STM-1) or STS-1 SONET/SDH Synchronous Payload Envelope (SPE). In the absence of transmit cells, the LASAR-155 automatically inserts Idle/unassigned cells into the SPE.

The LASAR-155 transmits SONET/SDH frames, via a bit serial interface, and formats SONET section, line, and path overhead appropriately. It performs framing pattern insertion (A1, A2), scrambling, alarm signal insertion, and creates section of PM7375, line, and path bit interleaved parity (B1, B2, B3) as required to allow performance monitoring at the far end. Line and path far end block error indications (Z2, G1) are also inserted. The LASAR-155 generates the payload pointer (H1, H2) and inserts the synchronous payload envelope which carries the ATM cell payload.

For system diagnostics, the LASAR-155 supports the insertion of a variety of errors into the transmit stream, such as framing pattern errors, bit interleaved parity errors and illegal pointers.

No auxiliary line clocks are required directly by the LASAR-155 as it is capable of synthesizing the line rate transmit clock and recovering the receive clock using either a 19.44 MHz or 6.48 MHz reference clock. The LASAR-155 is configured, controlled and monitored via either the generic microprocessor port interface in slave mode or the PCI bus interface in master mode. In slave mode, a mailbox scheme with shared buffers is provided for communication between the microprocessor and PCI Host.

The LASAR-155 can interface with external devices when the generic microprocessor port interface is configured for master mode operation. In this mode the PCI Host configures, controls and monitors the LASAR-155 and the external devices.

The LASAR-155 is implemented in low power, 0.6 micron, +5 Volt CMOS technology. It has TTL and pseudo ECL (PECL) compatible inputs and outputs and is packaged in a 208 pin copper slugged plastic QFP package.

PM7375 Data Sheet

PM7375 Data Sheet