Features: · Single chip dual ATM User-Network Interface operating at 155.52 and 51.84 Mbit/s. Also capable of operating at ATM Forum mid-range PHY subrates of 25.92 and 12.96 Mbit/s.

· Provides essential hardware and software compatibility with industry-standard PM5346 S/UNI-LITE device.

· Implements the ATM Forum User Network Interface Specification and the ATM physical layer for Broadband ISDN according to CCITT Recommendation I.432.

· Processes two duplex 155.52 Mbit/s STS-3c/STM-1 or 51.84 Mbit/s STS-1 data streams with on-chip clock and data recovery and clock synthesis.

· Provides Saturn Compliant Interface - PHYsical layer (SCI-PHY™) FIFO buffers in both transmit and receive paths with parity support. Compatible with ATM Forum Utopia Level 2 specification. The FIFOs may be independently bypassed.

· Inserts and extracts the generic flow control (GFC) bits via a simple serial interface and provides a transmit XOFF function to allow for local flow control.

· Supports 8-bit and 16-bit multi-PHY modes and a direct dual 8-bit mode.

· Provides a generic 8-bit microprocessor bus interface for configuration, control, and status monitoring.

· Provides a 4-bit output port for external alarms and control.

· Provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan test purposes.

· Low power, +5 Volt, CMOS technology.

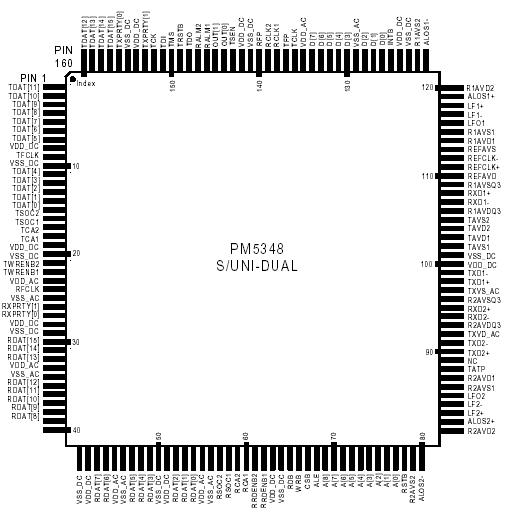

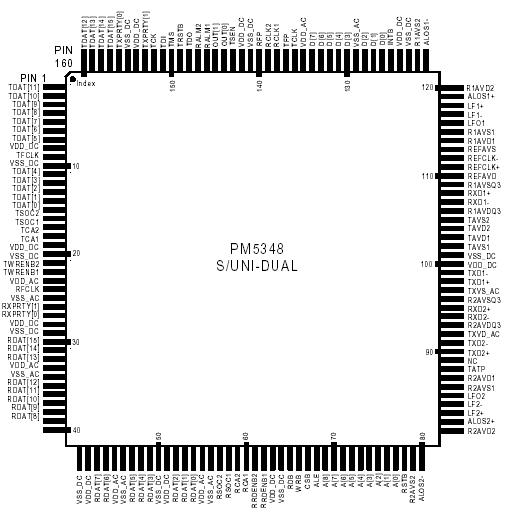

· 160 pin high performance plastic quad flat pack (MQFP) 28 mm x 28 mm package.

Application· Workstations and Personal Computers

· Switches and Hubs

· Routers

· SONET or SDH ATM InterfacesPinout SpecificationsAmbient Temperature under Bias . . . . .0°C to +70°C

SpecificationsAmbient Temperature under Bias . . . . .0°C to +70°C

Storage Temperature . . . . . . . . . . . .-40°C to +125°C

Supply Voltage . . . . . . . . . . . . . . . . . . . . -0.5V to +6.0V

Voltage on Any Pin . . . . . . . . . . . . . .-0.5V to VDD+0.5V

Static Discharge Voltage . . . . . . . . . . . . . . . . .±1000 V

Latch-Up Current . . . . . . . . . . . . . . . . . . . . . . .±100 mA

DC Input Current . . . . . . . . . . . . . . . . . . . . . . . .±20 mA

Lead Temperature . . . . . . . . . . . . . . . . . . . . . .+300°C

Absolute Maximum Junction Temperature . . . . . +150°CDescriptionThe PM5348 Dual SATURN User Network Interface (S/UNI-DUAL) is a monolithic integrated circuit that implements SONET/SDH processing and ATM mapping functions for two 155 Mbit/s or 51Mbit/s ATM User Network Interfaces. PM5348 is compliant with SONET and SDH requirements and ATM Forum User Network Interface specifications. The S/UNI-DUAL is software configurable, allowing feature selection without changes to external wiring.

The PM5348 S/UNI-DUAL receives two SONET/SDH channels via separate bit serial interfaces, recovers their corresponding clock and data, and processes section, line and path overhead for each channel. Each channel performs framing (A1,A2), descrambling, detects alarm conditions, and monitors section, line, and path bit interleaved parity (B1, B2, B3), accumulating error counts at each level for performance monitoring purposes. Line and path far end block error indications (M0 or M1, G1)PM5348 are also accumulated for each channel. Each channel of the S/UNI-DUAL interprets the received payload pointers (H1, H2) and extracts the synchronous payload envelope which carries the received ATM cell payload. Each channel of the S/UNI-DUAL frames to the ATM payload using cell delineation. HCS error correction is provided. Idle/unassigned cells may be dropped according to a programmable filter. Cells are also dropped upon detection of an uncorrectable header check sequence error. The PM5348 ATM cell payloads are descrambled. Legitimate ATM cells are written to a four cell FIFO

buffer.

The ATM PM5348 cells are read from each channel's FIFO via a synchronous interface with cell-based handshake using either a split 8 bit wide datapath, a direct 8 bit

wide datapath or a direct 16 bit wide datapath. Counts of received ATM cell headers that are errored and uncorrectable, those that are errored and correctable, and all passed cells are accumulated independently for each channel's performance monitoring purposes.

The PM5348 S/UNI-DUAL transmits two SONET/SDH channels via separate bit serial interfaces and formats section, line, and path overhead for each channel. Each channel performs framing pattern insertion (A1, A2), scrambling, alarm signal insertion, and creates section, line, and path bit interleaved parity (B1, B2, B3) as required to allow performance monitoring at the far end. Line and path far end block error indications (M0 or M1, G1) are also inserted.

Each channel of the PM5348 S/UNI-DUAL generates the payload pointer (H1, H2) and inserts the synchronous payload envelope which carries the ATM cell payload. PM5348 supports the insertion of a variety of errors into the transmit stream, such as framing pattern errors, bit interleaved parity errors, and illegal pointers, which are useful for system diagnostics.

ATM PM5348 cells are written to each channel's internally programmable-length 4-cell FIFO via a synchronous interface using either a split 8 bit wide datapath, a direct 8 bit wide datapath, or a direct 16 bit wide datapath. Idle/unassigned cells are automatically inserted when the internal FIFO contains less than one cell. Each channel of the PM5348 S/UNI-DUAL generates the header check sequence and scrambles the payload of the ATM cells. Payload scrambling can be disabled. No line rate clocks are required directly by the PM5348 S/UNI-DUAL as it synthesizes the transmit clock and recovers the receive clocks using a single 19.44 MHz or 6.48 MHz reference clock.

The PM5348 S/UNI-DUAL is configured, controlled and monitored via a generic 8-bit microprocessor bus interface. It is implemented in low power, +5 Volt CMOS technology. PM5348 has TTL and pseudo-ECL (PECL) compatible inputs and TTL/CMOS compatible outputs and is packaged in a 160 pin MQFP package.

PM5348 Data Sheet

PM5348 Data Sheet