Features: ` 27-MHz Master Clock Input

` Generated Audio System Clock: SCKO0: 768 fS (fS = 44.1 kHz) SCKO1: 384 fS, 768 fS (fS = 44.1 kHz) SCKO2: 256 fS (fS = 32, 44.1, 48, 64, 88.2, 96 kHz) SCKO3: 384 fS (fS = 32, 44.1, 48, 64, 88.2, 96 kHz)

` Zero PPM Error Output Clocks

` Low Clock Jitter: 50 ps (Typical)

` Multiple Sampling Frequencies: fS = 32, 44.1, 48, 64, 88.2, 96 kHz

` 3.3-V Single Power Supply

` PLL1705: Parallel Control PLL1706: Serial Control

` Package: 20-Pin SSOP (150 mil), Lead-Free ProductApplication· DVD Players

· DVD Add-On Cards for Multimedia PCs

· Digital HDTV Systems

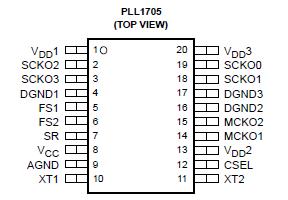

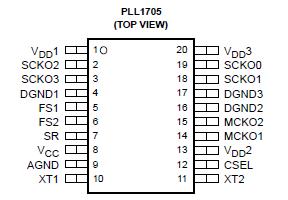

· Set-Top BoxesPinout Specifications

SpecificationsSupply voltage: VCC, VDD1VDD3 ...................................................4 V

Supply voltage differences: VCC, VDD1VDD3 ..............................±0.1 V

Ground voltage differences: AGND, DGND1DGND3 ......................±0.1 V

Digital input voltage: FS1 (MD), FS2 (MC), SR (MS), CSEL.............. 0.3 V to (VDD + 0.3) V

Analog input voltage, XT1, XT2 ...................................................... 0.3 V to (VCC + 0.3) V

Input current (any pins except supplies) ........................................±10 mA

Ambient temperature under bias ....................................................40°C to 125°C

Storage temperature ......................................................................55°C to 150°C

Junction temperature .........................................................................150°C

Lead temperature (soldering) ............................................................260°C, 5 s

Package temperature (IR reflow, peak) .............................................260°C

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated onditions for extended periods may affect device reliability.

DescriptionThe PLL1705† and PLL1706† are low cost, phase-locked loop (PLL) multiclock generators. The PLL1705 and PLL1706 can generate four system clocks from a 27-MHz reference input frequency. The clock outputs of the PLL1705 can be controlled by sampling frequency-control pins and those of the PLL1706 can be controlled through serial-mode control pins. The device gives customers both cost and space savings by eliminating external components and enables customers to achieve the very low-jitter performance needed for high performance audio DACs and/or ADCs. The PLL1705 and PLL1706 are ideal for MPEG-2 applications which use a 27-MHz master clock such as DVD players, DVD add-on cards for multimedia PCs, digital HDTV systems, and set-top boxes.

PLL1705 Data Sheet

PLL1705 Data Sheet