Number of Macrocells

: 8

Number of Programmable I/Os

: 8

Package / Case

: SOIC-20

Maximum Operating Temperature

: + 70 C

Minimum Operating Temperature

: 0 C

Operating Supply Voltage

: 3.3 V

Delay Time

: 25 ns

Logic Family

: PEEL

Supply Current

: 3 mA

Maximum Operating Frequency

: 38.4 MHz

Features: • Low Voltage, Ultra Low Power Operation

- Vcc = 2.7 to 3.6 V

- Icc = 5 µA (typical) at standby

- Icc = 1.5 mA (typical) at 1 MHz

- Meets JEDEC LV Interface Spec (JEDSD8-A)

- 5 Volts tolerant inputs and I/O's

• CMOS Electrically Erasable Technology

- Superior factory testing

- Reprogrammable in plastic package

- Reduces retrofit and development costs

• Application Versatility

- Replaces random logic

- Super set of standard PLDs

- Pin and JEDEC compatible with 16V8

- Ideal for battery powered systems

- Replaces expensive oscillators

• Architectural Flexibility

- Enhanced architecture fits in more logic

- 113 product terms x 36 input AND array

- 10 inputs and 8 I/O pins

- 12 possible macrocell configurations

- Asynchronous clear, Synchronous preset

- Independent output enables

- Programmable clock; pin 1 or p-term

- Programmable clock polarity

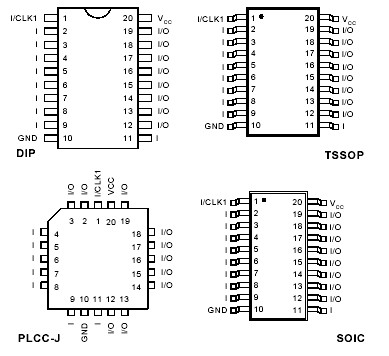

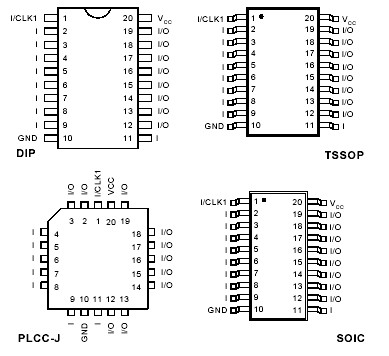

- 20 Pin DIP/SOIC/TSSOP and PLCC

- Schmitt triggers on clock and data inputs

• Schmitt Trigger Inputs

- Eliminates external Schmitt trigger devices

- Ideal for encoder designsPinout Specifications

Specifications

| Symbol |

Parameter |

Conditions |

Rating |

Unit |

|

VCC

VI,VO

IO

TST

TLT |

Supply Voltage

Voltage Applied to Any Pin2

Output Current

Storage Temperature

Lead Temperature |

Relative to Ground

Relative to Ground1

Per Pin (IOL, IOH)

Soldering 10 Seconds |

-0.5 to +6.0

-0.5 to +5.5

+25

-65 to +150

+300 |

V

V

mA

|

DescriptionThe PEEL18LV8Z is a Programmable Electrically Erasable Logic (PEEL) SPLD (Simple Programmable Logic Device) that operates over the supply voltage range of 2.7V-3.6V and features ultra-low, automatic "zero" power-down operation. The PEEL18LV8Z is logically and functionally similar to Anachip's 5V PEEL18CV8 and PEEL18CV8Z. The "zero power" (25 µA max. Icc) power-down mode makes the PEEL18LV8Z ideal for a broad range of batterypowered portable equipment applications, from hand-held meters to PCMCIA modems. EE-reprogrammability provides both the convenience of fast reprogramming for product development and quick product personalization in manufacturing, including Engineering Change Orders.

The differences between the PEEL18LV8Z and PEEL18CV8 include the addition of programmable clock polarity, p-term clock, and Schmitt trigger input buffers on all inputs, including the clock. Schmitt trigger inputs allow direct input of slow or noisy signals.

Like the PEEL18CV8, the PEEL18LV8Z is a logical superset of the industry standard PAL16V8 SPLD. The PEEL18LV8Z provides additional architectural features that allow more logic to be incorporated into the design. Anachip's JEDEC file translator allows easy conversion of existing 20 pin PLD designs to the PEEL18LV8Z architecture without the need for redesign. The PEEL18LV8Z architecture allows it to replace over twenty standard 20-pin DIP, SOIC, TSSOP and PLCC packages.

PEEL18LV8ZS-15L Data Sheet

PEEL18LV8ZS-15L Data Sheet