Features: Line Interface

• High density, generic interface for all E1/T1/J1 applications

• Analog receive and transmit circuitry for long haul and short haul applications

• Data and clock recovery using an integrated digital phase locked loop

• Maximum line attenuation up to -43 dB at 1024 kHz (E1) and up to -36 dB at 772 kHz (T1/J1)

• Programmable transmit pulse shapes for E1 and T1/J1 pulse masks

• Programmable line build-out for CSU signals according to ANSI T1.403 + FCC68 in steps of 0 dB, -7.5 dB, -15 dB and -22.5 dB (T1/J1)

• Low transmitter output impedances for high transmit return loss

• Tristate function of the analog transmit line outputs

• Transmit line monitor protecting the device from damage

• Jitter specifications of ITU-T I.431, G.703, G.736 (E1), G.823 (E1) and AT&T TR62411 (T1/J1) are met

• Optional crystal-less wander and jitter attenuation/compensation

• Dual rail or single rail digital inputs and outputs

• Unipolar NRZ or CMI coding for interfacing fibre optical transmission routes

• Selectable line codes (E1: HDB3, AMI - T1/J1: B8ZS, AMI with ZCS) for analog interface

• Loss of signal indication with programmable thresholds according to ITU-T G.775 and ETS300233 (E1)/ANSI T1.403, T1.231(T1/J1)

• Clock generator for jitter free system/transmit clocks

• Local loop and remote loop for diagnostic purposes

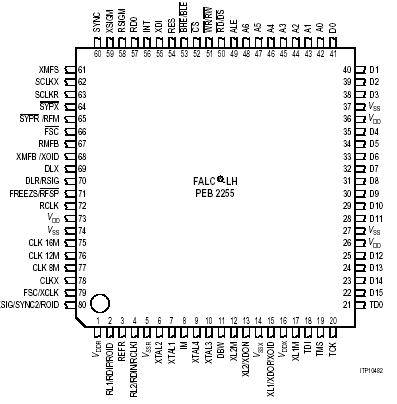

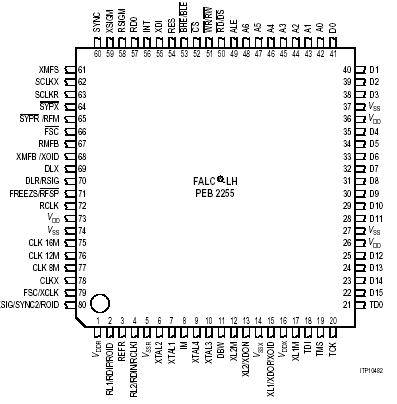

• Only one type of transformer (ratio 1:2) for E1 75/120 Ω and T1/J1 100/110 Ω P-MQFP-80-1

Frame Aligner

• Frame alignment/synthesis for 2048 kbit/s according to ITU-T G.704 (E1) and for

1544 kbit/s according to ITU-T G.704 and JT G.704 (T1/J1)

• Programmable frame formats :

E1: Doubleframe, CRC Multiframe (E1)

T1: 4-Frame Multiframe (F4,FT), 12-Frame Multiframe (F12, D3/4), Extended

Superframe (F24, ESF), Remote Switch Mode (F72, SLC96)

• Selectable conditions for recover/loss of frame alignment

• CRC4 to non-CRC4 interworking of ITU-T G. 706 Annex B (E1)

• Error checking via CRC4 procedures according to ITU-T G. 706 (E1)

• Error checking via CRC6 procedures according to ITU-T G. 706 and JT G.706 (T1/J1)

• Performs synchronization in ESF format according to NTT requirements (J1)

• Alarm and performance monitoring per second 16 bit counter for CRC-, framing errors, code violations, error monitoring via E bit and SA6 bit (E1), errored blocks, PRBS bit errors

• Insertion and extraction of alarm indication signals (AIS, Remote⁄Yellow Alarm, AUXP)

• IDLE code insertion for selectable channels

• 8.192 MHz/2.048 MHz (E1) or 8.192 MHz/1.544 MHz (T1/J1) system clock frequency

• Selectable 2048/4096 kbit/s backplane interface with programmable receive/transmit timeslot offset

• Programmable tristate function of 4096 kbit/s output via RDO

• Elastic store for receive and transmit route clock wander and jitter compensation; controlled slip capability and slip indication

• Programmable elastic buffer size: 2 frames/1 frame/short buffer/bypass

• Supports fractional E1 or T1 access

• Flexible transparent modes

• Programmable In-Band Loop Code detection and generation (TR62411)

• Channel loop back, line loop back or payload loop back capabilities (TR54016)

• Pseudo random bit sequence (PRBS) generator and monitor

• Provides loop-timed mode

• Clear channel capabilities (T1/J1)

Signaling Controller

• HDLC controller

Bit stuffing, CRC check and generation, flag generation, flag and address recognition,

handling of bit oriented functions, programmable preamble

• DL-channel protocol for ESF format according to ANSI T1.403 or according to AT&T

TR54016 (T1/J1)

• DL-channel protocol for F72 (SLC96) format

• CAS controller with last look capability, enhanced CAS- register access and freeze signaling indication

• Robbed bit signaling capability (T1/J1)

• Provides access to serial signaling data streams

• CAS Multiframe synchronization and synthesis according to ITU-T G.732

• Alarm insertion and detection (AIS and LOS in Timeslot 16)

• Transparent mode

• FIFO buffers (64 bytes deep) for efficient transfer of data packets.

• Time-slot assignment

Any combination of time slots selectable for data transfer independent of signaling

mode

Microprocessor Interface

• 8/16 bit microprocessor bus interface (Intel or Motorola type)

• All registers directly accessible (byte or word access)

• Multiplexed and non-multiplexed address bus operations

• Extended interrupt capabilities

• Hardware and software reset

• One second timer

General

• Boundary scan standard IEEE 1149.1

• P-MQFP-80 package; body size 14x14; pitch 0.65

• 5V power supply

• Typical power consumption 450 mW

Application• Wireless Basestations

• E1/T1/J1 ATM Gateways, Multiplexer

• E1/T1/J1 Channel & Data Service Units (CSU, DSU)

• E1/T1/J1 Internet Access Equipment

• LAN/WAN Router

• ISDN PRI, PABX

• Digital Access Cross Connect Systems (DACS)

• SONET/SDH Add/Drop MultiplexerPinout

PEB255 Data Sheet

PEB255 Data Sheet