Features: · Fully Synchronous Dynamic RAM, with all signals referenced to a positive clock edge

· Pulsed interface

· Possible to assert random column address in every cycle

· Quad internal banks controlled by BA0(A13) and BA1(A12)

· Byte control by LDQM and UDQM

· Programmable Wrap sequence (Sequential / Interleave)

· Programmable burst length (1, 2, 4, 8 and full page)

· Programmable /CAS latency (2 and 3)

· Ambient temperature (TA): -20 to + 70°C

· Automatic precharge and controlled precharge

· CBR (Auto) refresh and self refresh

· ×16 organization

· Single 3.3 V ± 0.3 V power supply

· LVTTL compatible inputs and outputs

· 4,096 refresh cycles / 64 ms

· Burst termination by Burst stop command and Precharge command

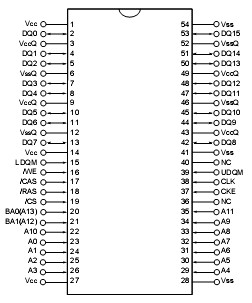

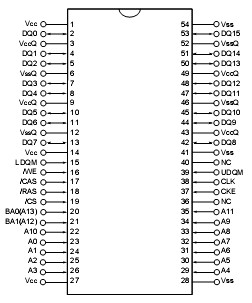

Pinout Specifications

Specifications

|

Parameter |

Symbol |

Condition |

Rating |

Unit |

| Voltage on power supply pin relative to GND |

VCC, VCCQ |

|

-0.5 to +4.6 |

V |

| Voltage on any pin relative to GND |

VT |

|

-0.5 to +4.6 |

V |

| Short circuit output current |

IO |

|

50 |

mA |

| Power dissipation |

PD |

|

1 |

W |

| Operating ambient temperature |

TA |

|

-20 to + 70 |

|

| Storage temperature |

Tstg |

|

-55 to + 125 |

|

Caution Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

DescriptionThe PD45128163-SU is high-speed 134,217,728-bit synchronous dynamic random-access memories, organized as 2,097,152 × 16 × 4 (word × bit × bank).

The synchronous DRAMs of PD45128163-SU achieved high-speed data transfer using the pipeline architecture.

All inputs and outputs of PD45128163-SU are synchronized with the positive edge of the clock.

The synchronous DRAMs of PD45128163-SU are compatible with Low Voltage TTL (LVTTL).

The PD45128163-SU is packaged in 54-pin TSOP (II).

PD45128163-SU Data Sheet

PD45128163-SU Data Sheet