Features: General

· The PCx509x is designed for GAP-compliant handsets and simple base stations

· Embedded 80C51 microcontroller with twice the performance of the classic architecture, up to 128 kbytes external memory or 64 kbytes FEEPROM program memory and 3 kbytes of data memory on chip. In addition there is 1 kbyte of on-chip data memory that is shared with on-chip Burst Mode Logic (BML) and DSP, the System Data RAM (SDR).

· 80C51 ports P0, P1, P2 and P3 available for interfacing to display, keyboard, I2C-bus, interrupt sources and/or external memory. External program memory is addressable up to 128 kbytes (PCD5090/xxx and PCA5097/xxx).

· Portable Part (PP) and Fixed Part (FP) modes

· TDMA frame (de)multiplexing; transmission or reception can be programmed for any slot

· Ciphering, scrambling, CRC checking/generation, protected B-fields

· Speech and data buffering space for six handsets

· Local call and B-field loop-back

· Two interrupt lines for BML and DSP to interrupt 80C51

· On-chip, three-channel time-multiplexed 8-bit Analog-to-Digital Converter (ADC) for RSSI measurement and battery voltage measurement. One channel available for other purposes.

· On-chip 8-bit DAC for frequency adjustment of 13.824 MHz on-chip crystal oscillator

· Phase error measurement and phase error correction by hardware

· Digital-to-Analog Converters (DACs) and ADCs for dynamic earpiece and dynamic or electret microphone

· On-chip reference voltage

· On-chip supply for electret microphone

· Very low ohmic buzzer output

· Serial interface to external ADPCM CODEC (PCD5032)

· IOM-2interface (Siemens registered trademark)

· Serial interface to synthesizer for frequency programming

· Programmable timing of radio-control signals

· Programmable polarity of radio-control signals

· Easy interfacing with radio circuits, operating at other supply voltage

· Programmable GMSK pulse shaper

· On-chip comparator for use as bit-slicer

· Power-on reset

· Low supply voltage (2.7 to 5.5 V)

· SACMOS technology.

DSP software features

· ADPCM encoding and decoding complying with G.721

· Speech filters

· Programmable gain in speech paths

· Side tone and soft mute

· Ringer and tone (DTMF) generator

· Dial tone detection

· Echo cancellation

· Automatic gain control

· Telephone Answering Machine (TAM) switch

· Conference call (PCD5090/400)

· Hands-free operation (PCD5090/311). For each DSP software version a separate manual is available, in which detailed information is provided on how parameters must be set.

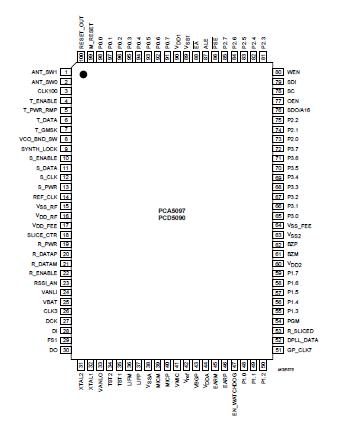

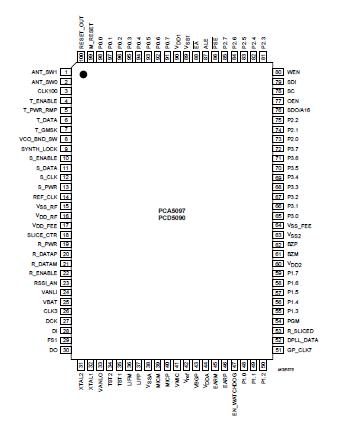

Pinout

DescriptionThe PCX509x is a family of single-chip controllers, designed for use in Digital Enhanced Cordless Telecommunications (DECT) systems. The family is designed for minimal component-count and minimum power consumption. All controllers include an embedded 80C51 microcontroller with on-chip memory and I2C-bus. The Philips DECT RF-Interface is implemented. The Burst Mode Logic performs the time-critical MAC layer functions for applications in DECT handsets and base stations. The ADPCM transcoding is in compliance with the CCITT recommendation G.721 and includes receive and transmit filters.

Power-on reset logic and power management functionsv of PCD5090 further reduce power consumption and external components. The chip is intended to support stand-alone systems only. There are no provisions of PCD5090 to build clusters of base stations. There are no provisions for external controllers to exert control over the embedded 80C51 or to have direct access to the on-chip data memories. The DECT controller consists of a number of functional blocks that operate more or less autonomously and communicate with each other via the System Data RAM (SDR). Blocks have access to SDR via the Internal System

Bus (ISB). The ISB PCD5090 consists of an 8-bit data, a 10-bit address bus and a number of bus-request/bus-grant signals. Access to the ISB is controlled by ISB bus Controller (IBC). The IBC acknowledges bus requests on the basis of a priority scheme. The embedded controller 80C51 is to be programmed by the user. It must contain DECT software from Man-Machine-Interface (MMI) to the DECT protocols TBC, CBC and DBC (refer to figures 10, 11, 12 and 13 in "prETS 300 175-2:1992 section 6").

All software of PCD5090 is available from Philips Semiconductors. Hardware state machines in the Burst Mode Logic (BML) and the Speech Interface (SPI) execute the lower blocks in the TBC, CBC and DBC. The 80C51 has control over theBML and the SPI via tables in SDR. The BML saves serial data, received via R_DATAP/M, in buffer areas in SDR. The position of buffers in SDR is fixed by the 80C51 software by means of tables previously mentioned.

PCD5090 Data Sheet

PCD5090 Data Sheet