Features: 28-pin versatile PAL programmable logic

device architectu

Electrically erasable CMOS technology

provides half power (only 115 mA) at high

speed (7.5 ns propagation delay)

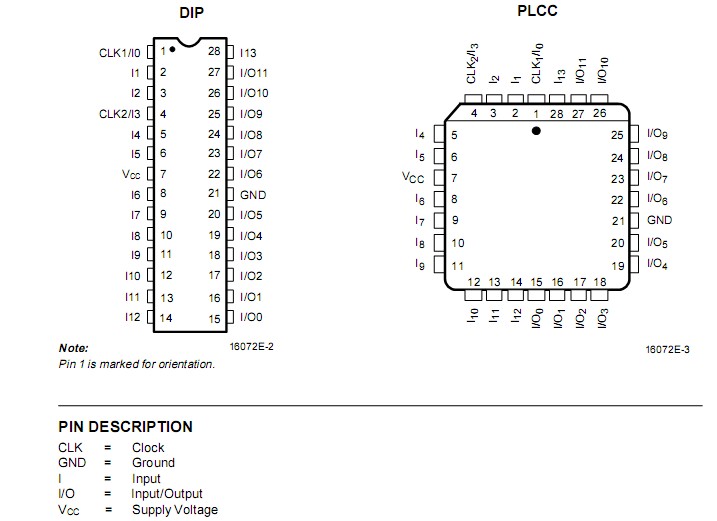

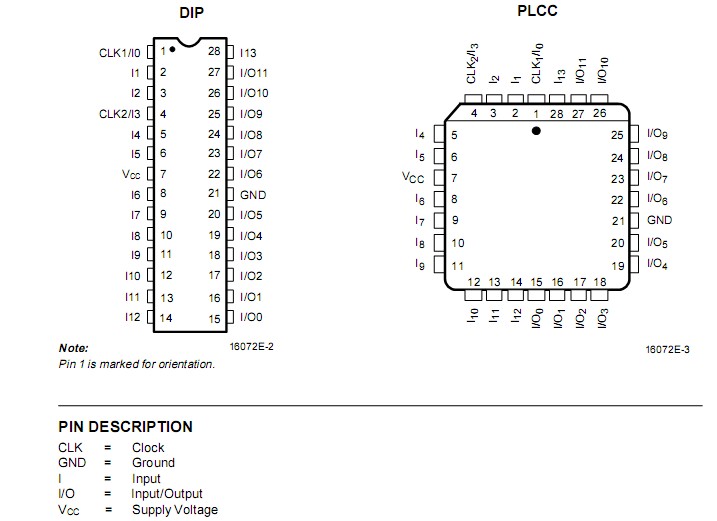

14 dedicated inputs and 12 input/output

macrocells for architectural flexibility

Macrocells can be registered or combinatorial,

and active high or active low

Varied product term distribution allows up to

16 product terms per output

Two clock inputs for independent functions

Global asynchronous reset and synchronous

preset for initialization

Register preload for testability and built-in

register reset on power-up

Space-efficient 28-pin SKINNYDIP and PLCC

packages

Center VCCand GND pins to improve signal

characteristics

Extensive third-party software and programmer

support through FusionPLD partnersPinout Specifications

SpecificationsStorage Temperature . . . . . . . . . . 65°C to +150°C

Ambient Temperature with

Power Applied. . . . . . . . . . . . . . . . 55°C to +125°C

Supply Voltage with

Respect to Ground. . . . . . . . . . . . . 0.5 V to +7.0 V

DC Input Voltage. . . . . . . . . . . . . . .0.6 V to +7.0 V

DC Output or I/O

Pin Voltage. . . . . . . . . . . . . . . 0.5 V to VCC+ 0.5 V

Static Discharge Voltage. . . . . . . . . . . . . . . . 2001 V

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

DescriptionThe PALCE26V12 is a 28-pin version of the popular PAL22V10 architecture. Built with low-power, high speed, electrically-erasable CMOS technology, the PALCE26V12 offers many unique advantages.

Device logic of PALCE26V12 is automatically configured according to the user's design specification. Design of PALCE26V12 is simplified by design software, allowing automatic creation of a programming file based on Boolean or state equations.The software can also be used to verify the design and can provide test vectors for the programmed device.

The PALCE26V12 utilizes the familiar sum-of-products (AND/OR) architecture that allows users to implement complex logic functions easily and efficiently. Multiple levels of combinatorial logic of PALCE26V12 can always be reduced to sum-of-products form, taking advantage of the very wide input gates available in PAL devices. The functions are programmed into the device through

electrically-erasable floating-gate cells in the AND logic array and the macrocells. In the unprogrammed state, all AND product terms float HIGH. If both true and complement of any input are connected, the term will be permanently LOW.

PALCE26V12 terms are connected to the fixed OR array with a varied distribution from 8 to 16 across the outputs (see Block Diagram). The OR sum of the products feeds the output macrocell. Each macrocell of PALCE26V12 can be programmed as registered or combinatorial, active high or active low, with registered I/O possible. The flip-flop can be clocked by one of two clock inputs. The output configuration is determined by four bits controlling three multiplexers in each macrocell.

AMD's FusionPLD program of PALCE26V12 allows PALCE26V12 designs to be implemented using a wide variety of popular industry-standard design tools. By working closely with the FusionPLD partners, AMD certifies that the tools provide accurate, quality support. By ensuring that third-party tools are available, costs are lowered because a designer does not have to buy a complete set

of new tools for each device. The FusionPLD program of PALCE26V12 also greatly reduces design time since a designer can use a tool that is already installed and familiar. Please refer to the PLD Software Reference Guide for certified development systems and the Programmer Reference Guide for approved programmers.

PALCE26V12 Data Sheet

PALCE26V12 Data Sheet