Features: · Single port 10 MHz Ethernet address parsing, filtering, and learning at wire speed

· Glue-free interface between the MUSIC LANCAM® Family and AMD, National, Motorola, or similar Ethernet Controllers having an NRZ serial data port

· Selectable filtering and learning decisions on DA and SA compares

· Supports aging with built-in LRU purge routine

· Supports cascaded MUSIC LANCAM series for long station lists

· Host processor port for LANCAM initialization and housekeeping activities

· Supports system clock rates from 20 MHz to 33 MHz

· Compatible with MU9C8328

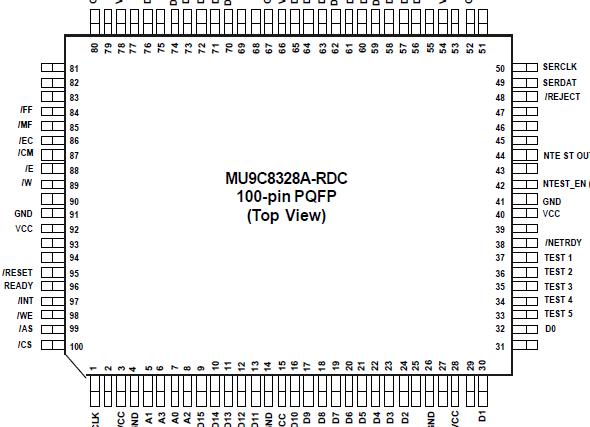

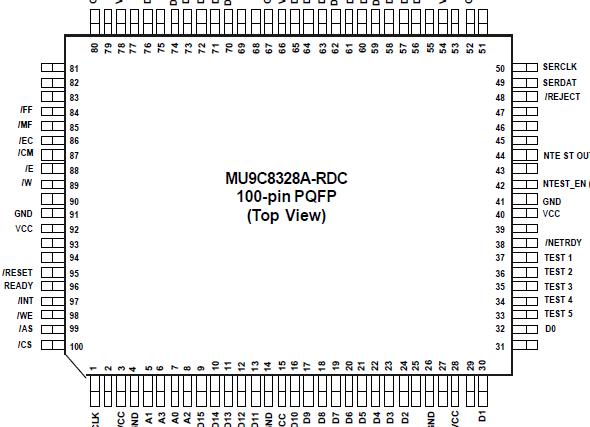

· 100-pin PQFP package

· 5 Volt operation

Pinout Specifications

SpecificationsSupply Voltage -0.5 Volts to 7.0 Volts

Voltage on all Other Pins -0.5 to VCC+0.5 Volts (-2.0 Volts for

10 ns, measured at the 50% point)

Temperature Under Bias -55°C to +125°C

Storage Temperature -55°C to +125°C

DC Output Current 20 mA (per Output, one at a time, one second duration)

Stresses exceeding those listed under Absolute Maximum Ratings may induce failure. Exposure to absolute maximum ratings for extended periods may reduce reliability. Functionality at or above these conditions is not implied.

All voltages are referenced to GND.

DescriptionThe MU9C8328A speeds up bridging operations using Ethernet controller chips with serial NRZ data outputs, such as AMD's MACE™, National's SONIC™, and Motorola's QUICC™ controllers, by parsing the Ethernet frame independently of the Ethernet controller device, and notifying it whether to accept or reject the incoming frame.

The MU9C8328A supports both positive and negative filtering on the Destination address and learning of new Source addresses, by efficiently controlling the compare activities of the MUSIC LANCAM Family. Filtering and learning routines are user configurable. These routines are automatically invoked by the internal state machine based on the contents of the incoming frame and the configuration settings. For aging and other housekeeping routines, the MU9C8328A provides the proper sequencing and timing of LANCAM accesses for an external processor.

The MU9C8328A receives serial NRZ data from the Ethernet controller chip, finds the Start delimiter, and loads the DA and SA into registers. The DA is sent to the LANCAM for filtering and, depending on the filter action selected, notifies the controller whether to copy or purge the frame. The SA is then sent to the LANCAM for comparison, and if no match is found, can be learned to the Next Free address in the LANCAM. Scheduling is done within the MU9C8328A so that each filtering action completes in the time of a minimum length frame. The filtering and learning routines are preprogrammed in the MU9C8328A, with decision options set in the Control register. A Status register is provided so the host processor can determine the results of activities. The specific Op-Code for the LANCAM learning instruction is by default a MOV NF, CR, V, but it can be overridden by writing a value to the Op-Code register. Aging and purging activity is directly controlled by the host processor. The READY signal notifies the host processor that processor operations are complete. The /INT signal notifies the processor that a network frame has been processed and the result stored in the Status register. The processor can turn off the network filtering activity to have total control of the LANCAM; during this time the controller can be notified to accept or reject all frames.

MU9C8328A Data Sheet

MU9C8328A Data Sheet