Features: • PC66-, PC100-, and PC133-compliant

• Fully synchronous; all signals registered on positive edge of system clock

• Internal pipelined operation; column address can be changed every clock cycle

• Internal banks for hiding row access/precharge

• Programmable burst lengths: 1, 2, 4, 8, or full page

• Auto Precharge, includes CONCURRENT AUTO PRECHARGE, and Auto Refresh Modes

• Self Refresh Modes: standard and low power

• 64ms, 4,096-cycle refresh

• LVTTL-compatible inputs and outputs

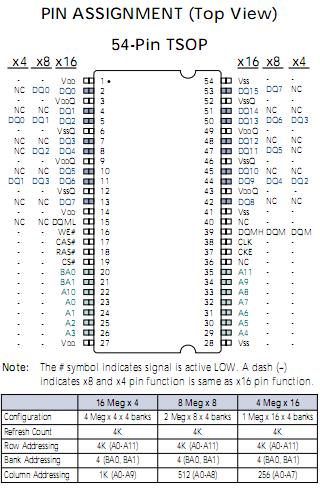

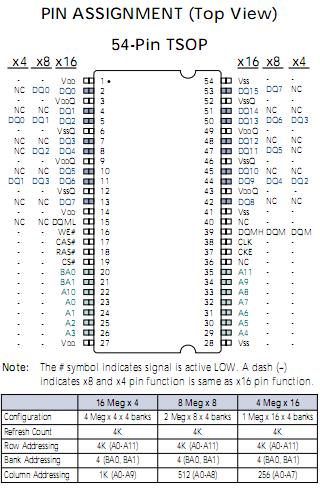

• Single +3.3V ±0.3V power supplyPinout Description

DescriptionThe Micron® 64Mb SDRAM MT48LC16M4A2 is a high-speed CMOS, dynamic random-access memory containing 67,108,864 bits. It is internally configured as a quad- bank DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CLK). Each of the x4's 16,777,216-bit banks of MT48LC16M4A2 is orga- nized as 4,096 rows by 1,024 columns by 4 bits. Each of the x8's 16,777,216-bit banks is organized as 4,096 rows by 512 columns by 8 bits. Each of the x16's 16,777,216- bit banks is organized as 4,096 rows by 256 columns by 16 bits.

Read and write accesses to the SDRAM MT48LC16M4A2 are burst oriented; accesses start at a selected location and con- tinue for a programmed number of locations in a pro- grammed sequence. Accesses begin with the registration of an ACTIVE command, which is then fol- lowed by a READ or WRITE command. The address bits registered coincident with the ACTIVE command are used to select the bank and row to be accessed (BA0, BA1 select the bank; A0-A11 select the row). The ad- dress bits of MT48LC16M4A2 registered coincident with the READ or WRITE

command are used to select the starting column loca- tion for the burst access

MT48LC16M4A2 Data Sheet

MT48LC16M4A2 Data Sheet