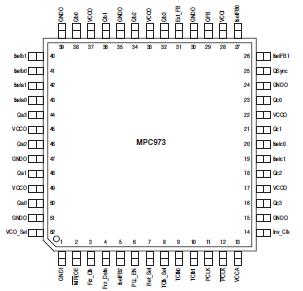

Pinout Specifications

Specifications

| Symbol |

Parameter |

Min |

Max |

Unit |

| VCC |

Supply Voltage |

0.3 |

4.6 |

V |

| VI |

Input Voltage |

0.3 |

VCC + 0.3 |

V |

| IIN |

Input Current |

|

±20 |

mA |

| TStor |

Storage Temperature Range |

-40 |

125 |

|

* Absolute maximum continuous ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute-maximum-rated conditions is not implied.

DescriptionThe MPC973 is a 3.3 V compatible, PLL based clock driver device targeted for high performance CISC or RISC processor based systems.

With output frequencies of up to 125 MHz and skews of 550 ps the MPC973 is ideally suited for most synchronous systems. The device offer twelve low skew outputs plus a feedback and sync output for added flexibility and ease of system implementation.

• Fully Integrated PLL

• Output Frequency up to 125 MHz

• Compatible with PowerPC and Pentium Microprocessors

• LQFP Packaging

• 3.3 V VCC

• ± 100ps Typical CycletoCycle Jitter

The MPC973 features an extensive level of frequency programmability between the 12 outputs as well as the input vs output relationships. Using the select lines output frequency ratios of 1:1, 2:1, 3:1, 3:2, 4:1, 4:3, 5:1, 5:2, 5:3, 6:1 and 6:5 between outputs can be realized by pulsing low one clock edge prior to the coincident edges of the Qa and Qc outputs. The Sync output will indicate when the coincident rising edges of the above relationships will occur. The selectability of the feedback frequency is independent of the output frequencies, this allows for very flexible programming of the input reference vs output frequency relationship. The output frequencies of MPC973 can be either odd or even multiples of the input reference. In addition the output frequency can be less than the input frequency for applications where a frequency needs to be reduced by a nonbinary factor. The PowerOn Reset ensures proper programming if the frequency select pins are set at power up. If the fselFB2 pin is held high, MPC973 may be necessary to apply a reset after powerup to ensure synchronization between the QFB output and the other outputs. The internal poweron reset is designed to provide this function, but with powerup conditions being dependent, MPC973 is difficult to guarantee. All other conditions of the fsel pins will automatically synchronize during PLL lock acquisition.

The MPC973 offers a very flexible output enable/disable scheme. This enable/disable scheme helps facilitate system debug as well as provide unique opportunities for system power down schemes to meet the requirements of "green" class machines. The MPC973 allows for the enabling of each output independently via a serial input port. When disabled or "frozen" the outputs will be locked in the "LOW" state, however the internal state machines will continue to run. Therefore when "unfrozen" the outputs will activate synchronous and in phase with those outputs which were not frozen. The freezing and unfreezing of outputs occurs only when they are already in the "LOW" state, thus the possibility of runt pulse generation is eliminated. A power-on reset will ensure that upon power up all of the outputs will be active. Note that all of the control inputs on the MPC973 have internal pullup resistors.

The MPC973 is fully 3.3 V compatible and requires no external loop filter components. All inputs accept LVCMOS/LVTTL

compatible levels while the outputs provide LVCMOS levels with the capability to drive 50 transmission lines. For series terminated lines each MPC973 output can drive two 50 lines in parallel thus effectively doubling the fanout of the device.

The MPC973 can consume significant power in some configurations. Users are encouraged to review Application Note

AN1545/D in the Advanced Clock Drivers Device Data book (DL207/D) for a discussion on the thermal issues with the MPC family of clock drivers.

MPC973 Data Sheet

MPC973 Data Sheet