Features: · 25 MHz to 400 MHz synthesized clock output signal

· Differential PECL output

· LVCMOS compatible control inputs

· On-chip crystal oscillator for reference frequency generation

· 3.3 V power supply

· Fully integrated PLL

· Minimal frequency overshoot

· Serial 3-wire programming interface

· Parallel programming interface for power-up

· 32-lead LQFP and 28-PLCC packaging

· 32-lead and 28-lead Pb-free package available

· SiGe Technology

· Ambient temperature range 0°C to +70°C

· Pin and function compatible to the MC12429 and MPC9229ApplicationUsing the Parallel and Serial Interface

The M and N counters can be loaded either through a parallel or serial interface. The parallel interface is controlled via the P_LOAD signal such that a LOW-to-HIGH transition will latch the information present on the M[8:0] and N[1:0] inputs into the M and N counters. When the P_LOAD signal is LOW the input latches will be transparent and any changes on the M[8:0] and N[1:0] inputs will affect the FOUT output pair. To use the serial port the S_CLOCK signal samples the information on the S_DATA line and loads it into a 14 bit shift

register. Note that the P_LOAD signal must be HIGH for the serial load operation to function. The Test register is loaded with the first three bits, the N register with the next two and

the M register with the final eight bits of the data stream on the S_DATA input. For each register the most significant bit is loaded first (T2, N1 and M8). A pulse on the S_LOAD pin after the shift register is fully loaded will transfer the divide values into the counters. The HIGH-to-LOW transition on the S_LOAD input will latch the new divide values into the

counters. Figure 4 illustrates the timing diagram for both a parallel and a serial load of the MPC92429 synthesizer. M[8:0] and N[1:0] are normally specified once at power-up through the parallel interface, and then possibly again through the serial interface. This approach allows the application to come up at one frequency and then change or fine-tune the clock as the ability to control the serial interface becomes available.

Using the Test and Diagnosis Output TEST

The TEST output provides visibility for one of the several internal nodes as determined by the T[2:0] bits in the serial configuration stream. It is not configurable through the parallel interface. Although it is possible to select the node that represents FOUT, the CMOS output is not able to toggle fast enough for higher output frequencies and should only be used for test and diagnosis. The T2, T1 and T0 control bits are preset to ‘000' when P_LOAD is LOW so that the PECL FOUT outputs are as jitter-free as possible. Any active signal on the TEST output pin will have detrimental affects on the jitter of the PECL output pair. In normal operations, jitter specifications are only guaranteed if the TEST output is static. The serial configuration port can be used to select one of the alternate functions for this pin. Most of the signals available on the TEST output pin are useful only for performance verification of the MPC92429 itself. However the PLL bypass mode may be of interest at the board level for functional debug. When T[2:0] is set to 110 the MPC92429 is placed in PLL bypass mode. In this mode the S_CLOCK input is fed directly into the M and N dividers. The N divider drives the FOUT differential pair and the M counter drives the TEST output pin. In this mode the S_CLOCK input could be used for low speed board level functional test or debug. Bypassing the PLL and driving FOUT directly gives the user more control on

the test clocks sent through the clock tree. Figure 6 shows the functional setup of the PLL bypass mode. Because the S_CLOCK is a CMOS level the input frequency is limited to

200 MHz. This means the fastest the FOUT pin can be toggled via the S_CLOCK is 100 MHz as the divide ratio of the Post-PLL divider is 2 (if N = 1). Note that the M counter output

on the TEST output will not be a 50% duty cycle.

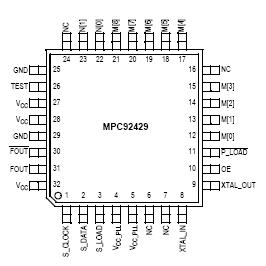

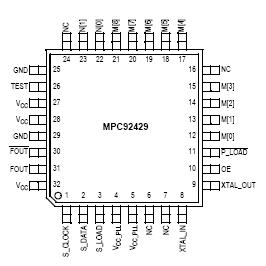

Pinout Specifications

Specifications

| Symbol |

Characteristics |

Min |

Max |

Unit |

Condition |

| VCC |

Supply Voltage |

–0.3 |

3.9 |

V |

|

| VIN |

DC Input Voltage |

–0.3 |

VCC + 0.3 |

V |

|

| VOUT |

DC Output Voltage |

–0.3 |

VCC + 0.3 |

V |

|

| IIN |

DC Input Current |

|

±20 |

mA |

|

| IOUT |

DC Output Current |

|

±50 |

mA |

|

| TS |

Storage Temperature |

-–65 |

125 |

°C |

|

1. Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these

conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated

conditions is not implied.DescriptionThe internal crystal oscillator MPC92429 uses the external quartz crystal as the basis of its frequency reference. The frequency of the internal crystal oscillator is divided by 16 and then multiplied by the PLL. The VCO within the PLL operates over a range of 800 to 1600 MHz. MPC92429's output is scaled by a divider that is configured by either the serial or parallel interfaces. The crystal oscillator frequency fXTAL, the PLL feedbackdivider M and the PLL post-divider N determine the output frequency.

The feedback path of the PLL is internal. The PLL adjusts the VCO output frequency of MPC92429 to be 4 x M times the reference frequency by adjusting the VCO control voltage. Note that for some values of M (either too high or too low) the PLL will not achieve phase lock. The PLL will be stable if the VCO frequency is within the specified VCO frequency range (800 to 1600 MHz). The M-value must be programmed by the serial or parallel interface.

The PLL post-divider N is configured through either the serial or the parallel interfaces, and can provide one of four division ratios (1, 2, 4, or 8). MPC92429 extends performance of the part while providing a 50% duty cycle. The output driver is driven differentially from the output divider, and is capable of driving a pair of transmission lines terminated 50 to VCC 2.0 V. The positive supply voltage for the internal PLL is separated from the power supply for the core logic and output drivers to minimize noise induced jitter.

The configuration logic of MPC92429 has two sections: serial and parallel. The parallel interface uses the values at the M[8:0] and N[1:0] inputs to configure the internal counters. MPC92429 is recommended on system reset to hold the P_LOAD input LOW until power becomes valid. On the LOW-to-HIGH transition of P_LOAD, the parallel inputs are captured. The parallel interface has priority over the serial interface. Internal pullup resistors are provided on the M[8:0] and N[1:0] inputs prevent the LVCMOS compatible control inputs from floating.

The serial interface centers on a fourteen bit shift register. The shift register shifts once per rising edge of the S_CLOCK input. The serial input S_DATA must meet setup and hold timing as specified in the AC Characteristics section of this document. The configuration latches will capture the value of the shift register on the HIGH-to-LOW edge of the S_LOAD input. See PROGRAMMING INTERFACE for more information. The TEST output reflects various internal node values, and is controlled by the T[2:0] bits in the serial data stream. In order to minimize the PLL jitter, it is recommended to avoid active signal on the TEST output.

MPC92429 Data Sheet

MPC92429 Data Sheet