Features: • 25 MHz to 400 MHz synthesized clock output signal

• Differential PECL output

• LVCMOS compatible control inputs

• On-chip crystal oscillator for reference frequency generation

• 3.3V power supply

• Fully integrated PLL

• Minimal frequency overshoot

• Serial 3-wire programming interface

• Parallel programming interface for power-up

• 32 lead LQFP and 28 PLCC packaging

• SiGe Technology

• Ambient temperature range 0

to +70

• Pin and function compatible to the MC12429

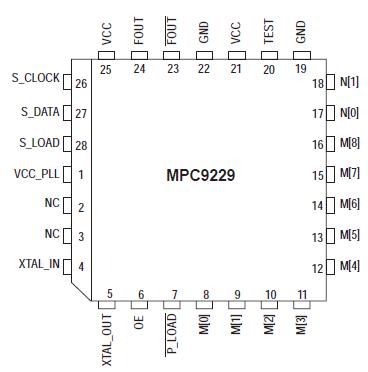

Pinout Specifications

Specifications

| Symbol |

Parameter |

Min |

Max |

Unit |

Condition |

| VCC |

Supply Voltage |

-0.3 |

3.9 |

V |

|

| VI |

DC Input Voltage |

-0.3 |

VCC + 0.3 |

V |

|

| VOUT |

DC Output Voltage |

-0.3 |

VCC + 0.3 |

V |

|

| IIN |

DC Input Current |

|

±20 |

mA |

|

| IOUT |

DC Output Current |

|

±50 |

mA |

|

| TS |

Storage Temperature |

-65 |

125 |

|

|

a. Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

Description

The internal crystal oscillator uses the external quartz crystal as the basis of its frequency reference. The frequency of the internal crystal oscillator is divided by 16 and then multiplied by the PLL. The VCO within the PLL operates over a range of 800 to 1600 MHz. MPC9229's output is scaled by a divider that is configured by either the serial or parallel interfaces. The crystal oscillator frequency fXTAL, the PLL feedback-divider M and the PLL post-divider N determine the output frequency.

The feedback path of the PLL is internal. The PLL adjusts the VCO output frequency to be 4VM times the reference frequency by adjusting he VCO control voltage. Note that for some values of M (either too high or too low) the PLL will not achieve phase lock. The PLL MPC9229 will be stable if the VCO frequency is within the specified VCO frequency range (800 to 1600 MHz). The M-value must be programmed by the serial or parallel interface.

The PLL post-divider N is configured through either the serial or the parallel interfaces, and can provide one of four division ratios (1, 2, 4, or 8). MPC9229 extends performance of the part while providing a 50% duty cycle. The output driver is driven differentially from the output divider, and MPC9229 is capable of driving a pair of transmission lines terminated 50W to VCC 2.0V. The positive supply voltage for the internal PLL is separated from the power supply for the core logic and output drivers to minimize noise induced jitter.

The configuration logic has two sections: serial and parallel. The parallel interface uses the values at the M[8:0] and N[1:0] inputs to configure the internal counters. MPC9229 is recommended on system reset to hold the P_LOAD input LOW until power becomes valid. On the LOWtoHIGH transition of P_LOAD, the parallel inputs are captured. The parallel interface has priority over the serial interface. Internal pullup resistors of MPC9229 are provided on the M[8:0] and N[1:0] inputs prevent the LVCMOS compatible control inputs from floating.

The serial interface centers on a fourteen bit shift register. The shift register shifts once per rising edge of the S_CLOCK input.

The serial input S_DATA must meet setup and hold timing as specified in the AC Characteristics section of MPC9229. The configuration latches will capture the value of the shift register on the HIGHtoLOW edge of the S_LOAD input. See the programming section for more information. The TEST output reflects various internal node values, and is controlled by the T[2:0] bits in the serial data stream. In order to minimize the PLL jitter, MPC9229 is recommended to avoid active signal on the TEST output.

MPC9229 Data Sheet

MPC9229 Data Sheet