Features: · Wide supply voltage range: 3.0V to 15V

· Guaranteed noise margin: 1.0V

· High noise immunity: 0.4 VCC (typ.)

· Low power: TTL compatibility: fan out of 2 driving 74L

· Expandable to 'N' stages

· Applicable to binary or BCD

· Low power pinout: 74L85

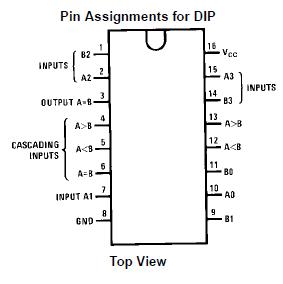

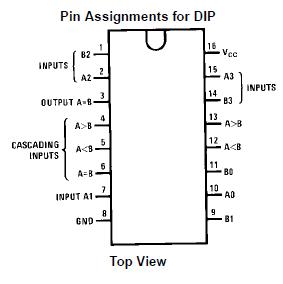

Pinout Specifications

Specifications

| Voltage at Any Pin |

-0.3V to VCC + 0.3V |

| Operating Temperature Range |

-40 to +85 |

| Storage Temperature Range |

-65 to +150 |

| Power Dissipation (PD) |

|

| Dual-In-Line |

700 mW |

| Small Outline |

500 mW |

| Operating VCC Range |

3.0V to 15V |

| VCC |

18V |

| Lead Temperature |

|

| (Soldering, 10 seconds) |

260 |

DescriptionThe MM74C85 is a four-bit magnitude comparator which will perform comparison of straight binary or BCD codes.

The circuit of MM74C85 consists of eight comparing inputs (A0, A1, A2, A3, B0, B1, B2, B3), three cascading inputs (A > B, A < B and A = B), and three outputs (A > B, A < B and A = B).

This MM74C85 compares two four-bit words (A and B) and determines whether they are "greater than," "less than," or "equal to" each other by a high level on the appropriate output.

For words greater than four-bits, units can be cascaded by connecting the outputs (A > B, A < B, and A = B) of the least significant stage to the cascade inputs (A > B, A < B and A = B) of the next-significant stage. In addition the least significant stage must have a high level voltage (VIN(1)) applied to the A = B input and low level voltage (VIN(0)) applied to A > B and A < B inputs.

MM74C85 Data Sheet

MM74C85 Data Sheet