Features: `COMPATIBLEWITH MK68000 CPU

`COMPATIBLEWITH MK68000 SERIES DMA's

`TWO INDEPENDENT FULL-DUPLEX CHAN. NELS

`TWO INDEPENDENT BAUD-RATE GENERATORS - Crystal oscillator input - Single-phase TTL clock input

`DIRECTLYADDRESSABLE REGISTERS

`all control registers are read/write)

`DATA RATE IN SYNCHRONOUS OR ASYNCHRONOUS MODES - 0-1.25M bits/second with 5.0MHz system clock rate

`SELF-TEST CAPABILITY

`RECEIVE DATA REGISTERS ARE QUADRUPLY BUFFERED ; TRANSMIT REGISTERS ARE DOUBLY BUFFERED

`DAISY-CHAIN PRIORITY INTERRUPT LOGIC PROVIDESAUTOMATIC INTERRUPT VECTO. RINGWITHOUT EXTERNAL LOGIC

`MODEMSTATUS CAN BE MONITORED - Separate modem controls for each channel

`ASYNCHRONOUS FEATURES - 5, 6, 7, or 8 bits/character - 1, 11/2, or 2 stop bits - Even, odd, or no parity - x1, x16, x32, and x64 clock modes - Break generation and detection - Parity, overrun, and framing error detection

`BYTE SYNCHRONOUSFEATURES - Internal or external character synchronization - One or two sync characters in separate registers - Automatic sync character insertion - CDC-16 or CRC-CCITT block check genera. tion and checking

`BIT SYNCHRONOUS FEATURES - Abort sequence generation and detection - Automatic zero insertion and deletion - Automatic flag insertion between messages - Address field recognition - I-field residue handling - Valid receive messages protected from overrun - CRC-16 or CRC-CCITT block check generation and checking

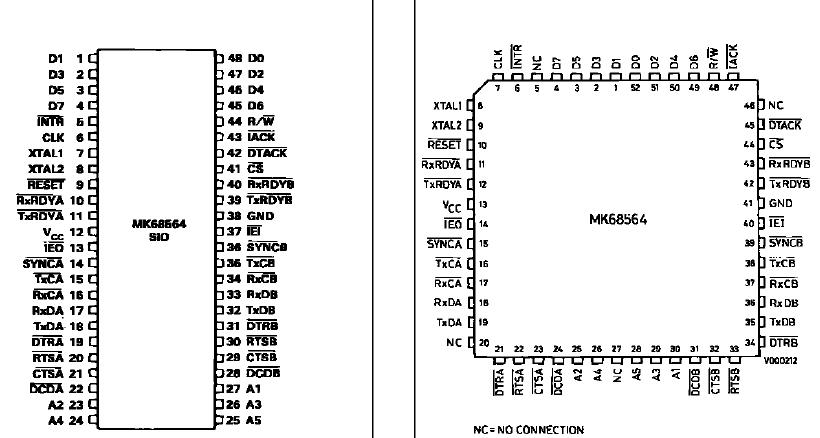

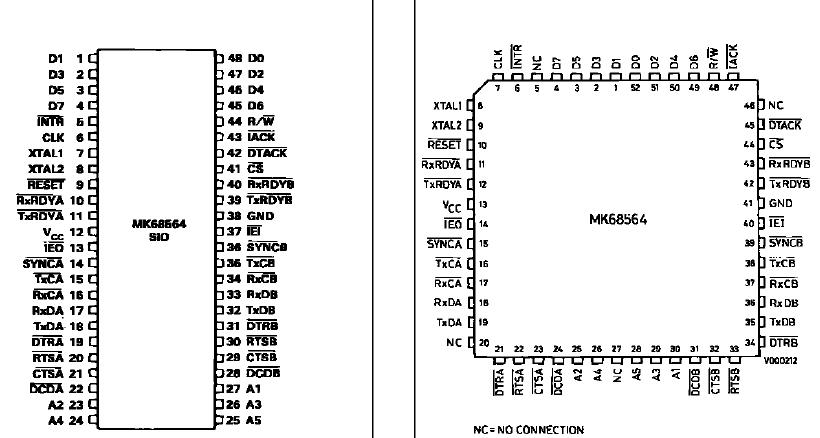

Pinout Specifications

Specifications

|

Symbol |

Parameter |

Value |

Unit |

| |

Temperature Under Bias |

-25 to +100 |

|

| |

Storage Temperature |

-65 to +150 |

|

| |

Voltage on any pin with respect to ground |

3 to 7 |

V |

| |

Power Dissipation |

1.5 |

W |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect evice reliabi-

DescriptionThe MK68564 SIO (Serial Input Output) is a dualchannel, multi-function peripheral circuit, designed to satisfy a wide variety of serial data communications requirements in microcomputer systems. Its basicfunction is a serial-to-parallel, parallel-to-serial converter/controller ; however within that role, it is systems software configurable so that its "personality" may be optimized for any given serial data communications application.

The MK68564 is capable of handling asynchronous protocols, synchronous byte-oriented protocols (such as IBM Bisync), and synchronous bit-oriented protocols (such as HDLC and IBM SDLC). This versatile device can also be used to support virtually any serial protocol for applications other than data communications (cassette or floppy disk interface, for example).

The MK68564 can generate and check CRC codes in any synchronous mode and may be programmed to check data integrity in various modes. The device also has facilities for modem controls in each channel. In applications where these controls are not needed, the modem controls may be used for general- purpose I/O.

MK68564 Data Sheet

MK68564 Data Sheet