Features: • Packaged in 20 pin SOIC

• 3.3 V + 5% operation

• Meets the TR62411, ETS300 011, and GR-1244 specification for MTIE, Pull-in/Hold-in Range, Phase Transients, and Jitter Generation for Stratum 3, 4,

and 4E

• Accepts multiple inputs: 8 kHz backplane clock, or 10 to 50 MHz

• Locks to 8 kHz + 100 ppm (External mode)

• Buffer Mode allows jitter attenuation of 10 - 50 MHz input and x1 / x0.5 or x1 / x2 outputs

• Exact internal ratios enable zero ppm error

• Output rates include T1, E1, T3, E3, and OC3 submultiples

• Available in Pb (lead) free package

• See also the MK2049-34 and MK2049-36ApplicationThe MK2049-45 is configured to generate a set of output frequencies from an 8 kHz input clock. Please refer to the Output Clock Selection Table on Page 2. Input bits FS3:0 are set according to this table, as is the external crystal frequency. Please refer to the Quartz Crystal section on this page regarding external crystal requirements.

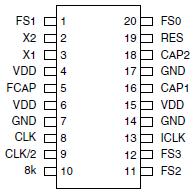

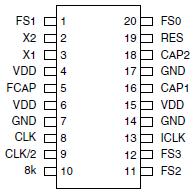

Pinout Specifications

SpecificationsStresses above the ratings listed below can cause permanent damage to the MK2049-45. These ratings, which are standard values for ICS commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

|

Item |

Rating |

| Supply Voltage, VDD |

7V |

| All Inputs and Outputs |

-0.5 V to VDD+0.5 V |

| Ambient Operating Temperature |

-40 to +85 |

| Storage Temperature |

-65 to +150 |

| Junction Temperature |

125 |

| Soldering Temperature |

250 |

DescriptionThe MK2049-45 is a dual Phase-Locked Loop (PLL) device which can provide frequency synthesis and jitter attenuation. The first PLL is VCXO based and uses a pullable crystal to track signal wander and attenuate input jitter. The second PLL is a translator for frequency multiplication. Basic configuration is determined by a Mode/Frequency Selection Table. Loop bandwidth and damping factor are programmable via external loop filter component selection.

Buffer Mode accepts a 10 to 50MHz input and will provide a jitter attenuated output at 0.5 x ICLK, 1 x ICLK or 2 x ICLK. In this mode the MK2049-45 is ideal for filtering jitter from high frequency clocks.

In External Mode, ICLK accepts an 8 kHz clock and will produce output frequencies from a table of common communciations clock rates, CLK and CLK/2. MK2049-45 allows for the generation of clocks frequency-locked to an 8 kHz backplane clock, simplifying clock synchronization in communications systems.

The MK2049-45 can be dynamically switched between T1, E1, T3, E3 outputs with the same 24.576 MHz crystal.

ICS MK2049-45 can customize these devices for many other different frequencies. Contact your ICS representative for more details.

MK2049-45 Data Sheet

MK2049-45 Data Sheet