Features: · Complete 900 MHz Band receiver on a monolithic IC

· UHF Frequency range 800 to 1000 MHz

· Typical range over 170 meters with monopole antenna

· Data rates to 5kbps (SWP), 20kbps (FIXED)

· Automatic tuning, no manual adjustment

· No Filters or Inductors required

· Low Operating Supply Current--4mA @ 868MHz

· Shutdown Mode for Duty-Cycle Operation in excess of 100:1

· Wakeup Function to Enable External Decoders and Microprocessors

· Very low RF re-radiation at the antenna

· CMOS logic interface to standard decoder and microprocessor ICs

· Extremely low external part countApplication· Automotive Remote Keyless Entry

· Security Systems

· Low Rate Data Modems

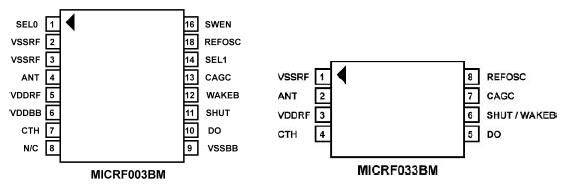

· Remote Meter Data CollectionPinout

| Pin Number |

Pin Name |

Pin Function |

|

1 |

SEL0 |

This pin, in conjunction with SEL1, programs the desired Demodulator Filter Bandwidth. This pin is internally

pulled-up to VDDRF. See Table 1. |

|

2/3 |

VSSRF |

This pin is the ground return for the RF section of the IC. The bypass capacitor connected from VDDRF to

VSSRF should have the shortest possible lead length. For best performance, connect VSSRF to VSSBB at the

power supply only (i.e., keep VSSBB currents from flowing through VSSRF return path). |

|

(1) |

VSSRF |

This pin is the ground return for the IC. The bypass capacitor connected from VDDRF to VSSRF should have

the shortest possible lead length. |

|

4

(2) |

ANT |

This is the receive RF input, internally ac-coupled. Connect this pin to the receive antenna. Input impedance is

high (FET gate) with approximately 2pF of shunt (parasitic) capacitance. For applications located in high

ambient noise environments, a fixed value band-pass network may be connected between the ANT pin and

VSSRF to provide additional receive selectivity and input overload protection. (See "Application Note TBD".) |

|

5 |

VDDRF |

This pin is the positive supply input for the RF section of the IC. VDDBB and VDDRF should be connected

directly at the IC pins. Connect a low ESL, low ESR decoupling capacitor from this pin to VSSRF, as short as

possible. |

|

6 |

VDDBB |

This pin is the positive supply input for the baseband section of the IC. VDDBB and VDDRF should be

connected directly at the IC pins. |

|

(3) |

VDDRF |

This pin is the positive supply input for the IC. Connect a low ESL, low ESR decoupling capacitor from this pin

to VSSRF, as short as possible. |

|

7

(4) |

CTH |

This pin is the positive supply input for the IC. Connect a low ESL, low ESR decoupling capacitor from this pin

to VSSRF, as short as possible. |

|

8 |

N/C |

Unused Pin |

|

9 |

VSSBB |

This is the ground return for the baseband section of the IC. The bypass and output capacitors connected to

VSSBB should have the shortest possible lead lengths. For best performance, connect VSSRF to VSSBB at

the power supply only (i.e., keep VSSBB currents from flowing through VSSRF return path). |

|

10

(5) |

DO |

The output data signal. CMOS level compatible. |

|

11

(6) |

SHUT |

A logic input for Shutdown Mode control. Pull this pin low to place the IC into operation. This pin in internally

pulled-up to VDDRF. |

|

12 |

WAKEB |

An output signal, active low when the IC detects an incoming RF signal, determined by monitoring for data

preamble. CMOS level compatible. |

|

13

(7) |

CAGC |

Integrating capacitor for on-chip AGC (Automatic Gain Control). The Decay/Attack time-constant (TC) ratio is

nominally set as 10:1. Use of 0.47uF or greater is strongly recommended for best range performance. Use

low-leakage type capacitors for duty-cycle operation (Dip Tantalum, Ceramic, Polyester). (See "Application Note

TBD.) |

|

14 |

SEL1 |

This pin, in conjunction with SEL0, programs the desired Demodulator Filter Bandwidth. This pin in internally

pulled-up to VDDRF. See Table 1. |

|

15

(8) |

REFOSC |

This is the timing reference for on-chip tuning and alignment. Connect either a ceramic resonator or crystal

(mode dependent) between this pin and VSSBB, or drive the input with an AC coupled 0.5Vpp input clock. Use

ceramic resonators without integral capacitors. Note that if operating in FIXED mode, a crystal must be used;

however in SWP mode, one may use either a crystal or ceramic resonator. See "Application Note TBD" for

details on frequency selection and accuracy. |

|

16 |

SWEN |

This logic pin controls the operating mode of the MICRF003. When SWEN = HIGH, the MICRF003 is in SWP

mode. When SWEN = LOW, the device operates as a conventional single-conversion superheterodyne

receiver. (See "Application Note TBD" for details.) This pin is internally pulled-up to VDDRF. |

SpecificationsSupply Voltage (VDDRF, VDDBB)....................................+7V

Voltage on any I/O Pin.........................VSS-0.3 to VDD+0.3

Junction Temperature.............................................+150°C

Storage Temperature Range..................-65°C to + 150°C

Lead Temperature (soldering, 10 seconds)...........+ 260°CDescriptionThe MICRF003 is a single chip OOK (ON-OFF Keyed) Receiver IC for remote wireless applications, employing Micrel's latest QwikRadiotm technology. This device is a true "antenna-in, data-out" monolithic device. All RF and IF tuning is accomplished automatically within the IC, which eliminates manual tuning, and reduces production costs. Receiver functions are completely integrated. The result is a highly reliable yet extremely low cost solution for high volume wireless applications. Because the MICRF003 is a true single-chip radio receiver, it is extremely easy to apply, minimizing design and production costs, and improving time to market. The MICRF003 provides two fundamental modes of operation, FIXED and SWP. In FIXED mode, the device functions like a conventional Superheterodyne receiver, with an (internal) local oscillator fixed at a single frequency based on an external reference crystal or clock. As with any conventional superheterodyne receiver, the transmit frequency must be accurately controlled, generally with a crystal or SAW (Surface Acoustic Wave) resonator.

In SWP mode, the MICRF003 sweeps the (internal) local oscillator at rates greater than the baseband data rate. This effectively "broadens" the RF bandwidth of the receiver to a value equivalent to conventional superregenerative receivers. Thus the MICRF003 can operate with less expensive LC transmitters without additional components or tuning, even though the receiver topology is still superheterodyne. In this mode the reference crystal can be replaced with a less expensive ± 0.5% ceramic resonator.

The MICRF003 provides two additional key features: (1) a Shutdown Mode, which may be used for duty-cycle operation, and (2) a "Wakeup" function, which provides a logical indication of an incoming RF signal. These features make the MICRF003 ideal for low and ultra-low power applications, such as RKE and RFID.

All post-detection (demodulator) data filtering is provided on the MICRF003, so no external filters need to be designed. Any one of four filter bandwidths may be selected externally by the user. Nominal filter bandwidths range in binary steps, from 0.75kHz to 6kHz (SWP mode) or 2.8kHz to 22.4kHz (FIXED mode). The user of MICRF003 only needs to program the appropriate filter selection based on data rate and code modulation format.

MICRF003 Data Sheet

MICRF003 Data Sheet