Features: Diode Protection on All Inputs

Supply Voltage Range = 3.0 Vdc to 18 Vdc

Internally Synchronous for High Speed

Logic EdgeClocked Design - Count Occurs on Positive Going

Edge of Clock

Single Pin Reset

Asynchronous Preset Enable Operation

Capable of Driving Two LowPower TTL Loads or One LowPower

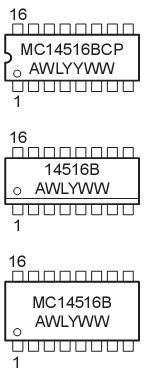

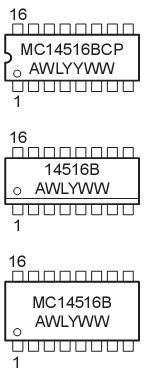

Schottky Load Over the Rated Temperature RangePinout Specifications

Specifications

| Symbol |

Parameter |

Value |

Unit |

| VDD |

DC Supply Voltage Range |

0.5 to +18.0 |

V

|

| VIN,VOUT |

Input or Output Voltage Range

(DC or Transient) |

0.5 to VDD + 0.5

|

V |

| IIN,IOUT |

Input or Output Current

(DC or Transient) per Pin |

±10 |

mA |

| PD |

Power Dissipation,

per Package (Note 3.) |

500 |

mW |

| TA |

Ambient Temperature Range |

55 to +125 |

|

| Tstg |

Storage Temperature Range |

65 to +150 |

|

| TL |

Lead Temperature

(8Second Soldering) |

260 |

|

DescriptionThe MC14516B synchronous up/down binary counter is constructed with MOS Pchannel and Nchannel enhancement mode devices in a monolithic structure.

This counter MC14516B can be preset by applying the desired value, in binary, to the Preset inputs (P0, P1, P2, P3) and then bringing the Preset Enable (PE) high. The direction of counting is controlled by applying a high (for up counting) or a low (for down counting) to the UP/DOWN input. The state of the counter MC14516B changes on the positive transition of the clock input.

Cascading MC14516B can be accomplished by connecting the Carry Out to the Carry INof the next stage while clocking each counter in parallel. The outputs (Q0, Q1, Q2, Q3) can be reset to a low state by applying a high to the reset (R) pin.

This CMOS counter finds primary use in up/down and difference counting. Other applications of MC14516B include: (1) Frequency synthesizer applications where low power dissipation and/or high noise immunity is desired, (2) Analogtodigital and digitaltoanalog conversions, and (3) Magnitude and sign generation.

MC14516 Data Sheet

MC14516 Data Sheet