Features: •1:10 differential clock distribution

•35 ps maximum device skew

•Fully differential architecture from input to all outputs

•SiGe:C technology supports near-zero output skew

•Supports DC to 2.7 GHz operation of clock or data signals

•ECL/PECL compatible differential clock outputs

•ECL/PECL/HSTL compatible differential clock inputs

•Single 3.3V, -3.3V, 2.5V or -2.5V supply

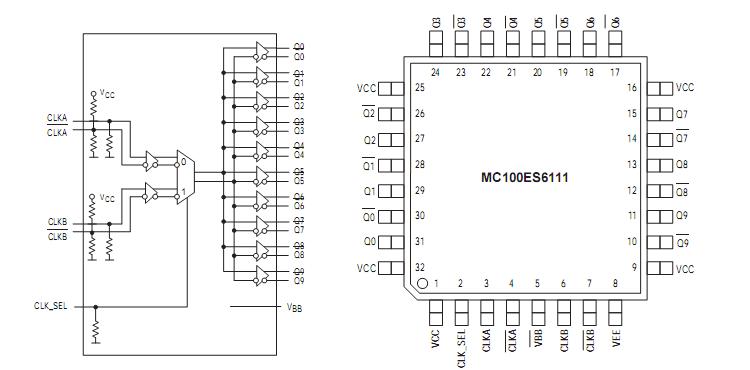

•Standard 32 lead LQFP package

•Industrial temperature range

•Pin and function compatible to the MC100EP111ApplicationTo make the optimum use of high clock frequency and low skew capabilities of the MC100ES6111, the MC100ES6111 is specified, characterized and tested for the junction temperature range of TJ=0°C to +110°C. Because the exact thermal performance depends on the PCB type, design, thermal management and natural or forced air convection,the junction temperature provides an exact way to correlate the application specific conditions to the published performance data of this datasheet. The correlation of the junction temperature range to the application ambient temperature range and vice versa can be done by calculation:

The MC100ES6111 guarantees low output-to-output bank skew of 35 ps and a part-to-part skew of max. 250 ps. To ensure low skew clock signals in the application, both outputs of any differential output pair need to be terminated identically, even if only one output is used. When fewer than all nine output pairs are used, identical termination of all output pairs within the output bank is recommended. If an entire output bank is not used, it is recommended to leave all of these outputs open and unterminated. This will reduce the device power consumption while maintaining minimum

output skew.

Pinout Specifications

Specifications

| Symbol |

Characteristics

|

Min

|

Max |

Unit |

Vcc

|

Supply Voltage

|

-0.3

|

3.6

|

V |

VIN

|

DC Input Voltage

|

-0.3

|

VCC+ 0.3

|

V |

Vout

|

Output Voltage

|

-0.3

|

Vcc+ 0.3

|

V |

Iin

|

DC Input Current

|

|

±20

|

mA |

IOUT

|

DC Output Current

|

|

±50 |

mA |

TS

|

Storage temperature

|

-65

|

125

|

|

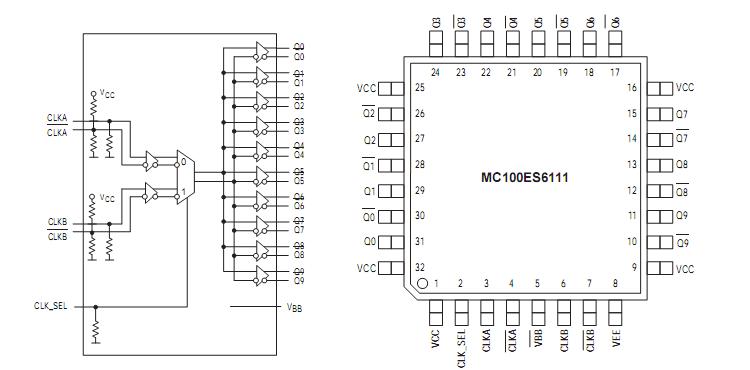

DescriptionThe MC100ES6111 is designed for low skew clock distribution systems and supports clock frequencies up to 2.7 GHz. The device accepts two clock sources. The CLKA input can be driven by ECL or PECL compatible signals, the CLKB input accepts HSTL compatible signals. The selected input signal is distributed to 10 identical, differential ECL/PECL outputs. If VBB is connected to the CLKA input and bypassed to GND by a 10 nF capacitor, the MC100ES6111 can be driven by single-ended ECL/PECL signals utilizing the VBB bias voltage output.

In order to meet the tight skew specification of the device, both outputs of a differential output pair should be terminated, even if only one out pisused.In the case where notal ltenout putsare used, the output pairs on the same package side as the parts being used on that side should be terminated.

The MC100ES6111 can be operated from a single 3.3V or 2.5V supply. As most other ECL compatible devices, the MC100ES6111 supports positive (PECL) and negative (ECL) supplies. The MC100ES6111 is pin and function compatible to the MC100EP111.

MC100ES6111 Data Sheet

MC100ES6111 Data Sheet