Output Type

:

Minimum Operating Temperature

: - 40 C

Packaging

: Reel

Number of Circuits

: 1

Counter Type

: Binary

Counting Sequence

: Up

Maximum Operating Temperature

: + 70 C

Number of Input Lines

: 8

Logic Family

: ECL

Logic Type

: ECL

Package / Case

: LQFP-32

Propagation Delay Time

: 0.7 ns

Features: 550 ps Typical Propagation Delay

Operation Frequency > 1.3 GHz is 30% Faster than MC100EP016

PECL Mode Operating Range: VCC= 3.0 V to 3.6 V with VEE= 0 V

NECL Mode Operating Range: VCC= 0 V with VEE= −3.0 V to −3.6 V

Open Input Default State

Safety Clamp on Clock Inputs

Internal TC Feedback (Gated)

Addition of COUT and COUT

8−Bit

Differential Clock Input

VBB Output

Fully Synchronous Counting and TC Generation

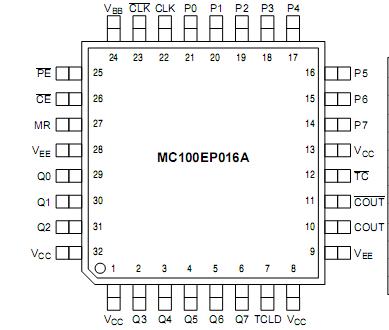

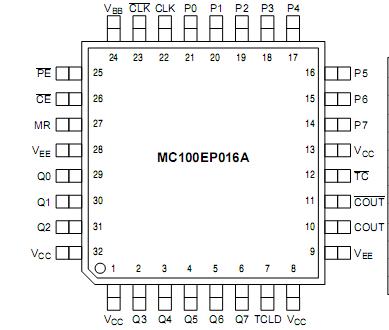

Asynchronous Master ResetPinout Specifications

Specifications

| Symbol |

Parameter |

Condition 1 |

Condition2 |

Rating |

Units |

| VCC |

PECL Mode Power Supply |

VEE= 0 V |

|

6 |

V |

| VEE |

NECL Mode Power Supply |

VCC= 0 V |

|

-6 |

V |

| VI |

PECL Mode Input Voltage

PECL Mode Inut Voltage |

VEE= 0 V

VCC= 0 V |

VIVCC

CIVEE

|

6

-6 |

V

V |

| IOUT |

Output Current |

Continuous

Surge

|

|

50

100 |

mA

mA |

| IBB |

VBB Sink/Source |

|

|

+0.5 |

mA |

| TA |

Operating Temperature Range |

|

|

−40to +70 |

09

|

| TSTG |

Storage Temperature Range |

|

|

−65to+150 |

|

| QJA |

Thermal Resistance (Junction to Ambient) |

0 LFPM

500LFPM |

32 LQFP

32 LQFP |

74

61 |

/W

/W |

| QJC |

Thermal Resistance (Junction to Case) |

std bd |

32 LQFP |

12 to 17 |

/W |

| TSOI |

Wave Solder |

<2 to 3 sec @ 248 |

|

265 |

|

DescriptionThe MC100EP016AFAR2 is a high−speed synchronous, presettable, cascadeable 8−bit binary counter. Architecture and operation are the same as the ECLinPSfamily MC100E016 with higher operatingspeed.

The MC100EP016AFAR2 features internal feedback to TC gated by the TCLD (Terminal Count Load) pin. When TCLD is LOW (or left open, in which case it is pulled LOW by the internal pulldowns), the TC feedback is disabled, and counting proceeds continuously, with TC going LOW to indicate an all−one state. When TCLD is HIGH, the TC feedback causes the counter to automatically reload upon TC = LOW, thus functioning as a programmable counter. The Qn outputs do not need to be terminated for the count function to operate properly. To minimize noise and power, unused Q outputs should be left unterminated.

COUT and COUT provide differential outputs from a single, non−cascaded counter or divider application. COUT and COUT should not be used in cascade configuration. Only TC should be used for a MC100EP016AFAR2 or divider cascade chain output.

A differential clock input has also been added to improve performance.

The 100 Series contains temperature compensation.

Parameters: | Technical/Catalog Information | MC100EP016AFAR2 |

| Vendor | ON Semiconductor |

| Category | Integrated Circuits (ICs) |

| Logic Type | Binary Counter |

| Trigger Type | Positive, Negative |

| Voltage - Supply | 3 V ~ 3.6 V |

| Number of Bits per Element | 8 |

| Number of Elements | 1 - Single |

| Direction | Up |

| Mounting Type | Surface Mount |

| Package / Case | 32-LQFP |

| Reset | Asynchronous |

| Packaging | Tape & Reel (TR) |

| Operating Temperature | -40°C ~ 70°C |

| Count Rate | 1.4GHz |

| Timing | Synchronous |

| Lead Free Status | Contains Lead |

| RoHS Status | RoHS Non-Compliant |

| Other Names | MC100EP016AFAR2

MC100EP016AFAR2

MC100EP016AFAOSTR ND

MC100EP016AFAOSTRND

MC100EP016AFAOSTR

|

MC100EP016AFAR2 Data Sheet

MC100EP016AFAR2 Data Sheet