High Level Output Current

:

Low Level Output Current

:

Mounting Style

: SMD/SMT

Maximum Operating Temperature

: + 85 C

Packaging

: Tube

Output Type

: Differential

Polarity

: Inverting, Non-Inverting

Input Type

: Differential

Logic Family

: ECL

Logic Type

: ECL

Supply Voltage - Max

: 5.7 V

Package / Case

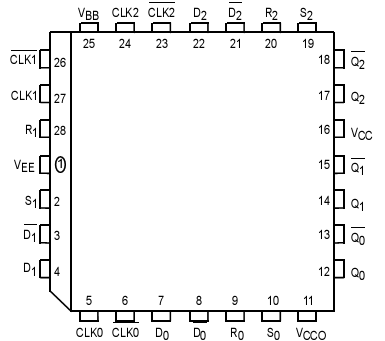

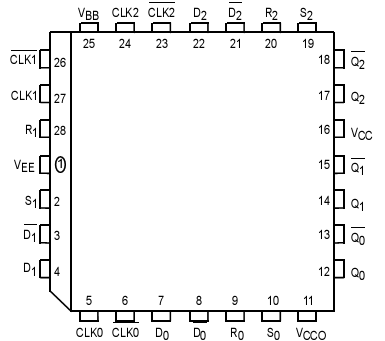

: PLCC-28

Number of Circuits

: 3

Propagation Delay Time

: 0.85 ns

Features: ` Edge-Triggered Asynchronous Set and Reset

` Differential D, CLK and Q; VBB Reference Available

` 1100MHz Min. Toggle Frequency

` Extended 100E VEE Range of 4.2V to 5.46VPinout Description

DescriptionThe MC100E431FN is a 3-bit flip-flop with differential clock, data input and data output.

The asynchronous Set and Reset controls are edge-triggered rather than level controlled. This allows the user to rapidly set or reset the flip-flop and then continue clocking at the next clock edge, without the necessity of de asserting the set/reset signal (as would be the case with a level controlled set/reset).

The MC100E431FN is also designed with larger internal swings, an approach intended to minimize the time spent crossing the threshold region and thus reduce the metastability susceptibility window.

The differential input structures are clamped so that the inputs of unused registers can be left open without upsetting the bias network of the MC100E431FN. The clamping action will assert the D and the CLK sides of the inputs. Because of the edge triggered flip-flop nature of the device simultaneously opening both the clock and data inputs will result in an

output which reaches an unidentified but valid state. Note that the input clamps only operate when both inputs fall to 2.5V below VCC

MC100E431FN Data Sheet

MC100E431FN Data Sheet