Features: ` High-performance 3.3-V EEPROM-based programmable logic devices (PLDs) built on second-generation Multiple Array MatriX (MAX®) architecture (see Table 1)

` 3.3-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface with advanced pin-locking capability

MAX 7000AE device in-system programmability (ISP) circuitry compliant with IEEE Std. 1532

EPM7128A and EPM7256A device ISP circuitry compatible with IEEE Std. 1532

` Built-in boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1

` Supports JEDEC Jam Standard Test and Programming Language (STAPL) JESD-71

` Enhanced ISP features

Enhanced ISP algorithm for faster programming (excluding EPM7128A and EPM7256A devices)

ISP_Done bit to ensure complete programming (excluding EPM7128A and EPM7256A devices)

Pull-up resistor on I/O pins during in-system programming

` Pin-compatible with the popular 5.0-V MAX 7000S devices

` High-density PLDs ranging from 600 to 10,000 usable gates

` Extended temperature rangePinout Specifications

Specifications

|

Symbol |

Parameter |

Conditions |

Min |

Max |

Unit |

|

VCC |

Supply voltage |

With respect to ground (2) |

-0.5 |

4.6 |

V |

|

VI |

DC input voltage |

-2.0 |

5.75 |

V |

|

IOUT |

DC output current, per pin |

|

-25 |

25 |

mA |

|

TSTG |

Storage temperature |

No bias |

-65 |

150 |

|

|

TA |

Ambient temperature |

Under bias |

-65 |

135 |

|

|

TJ |

Junction temperature |

BGA, FineLine BGA, PQFP, and

TQFP packages, under bias |

|

135 |

|

DescriptionMAX 7000A devices are high-density, highperformance devices based on Altera's second-generation MAX architecture. Fabricated with advanced CMOS technology, the EEPROMbased MAX 7000A devices operate with a 3.3-V supply voltage and provide 600 to 10,000 usable gates, ISP, pin-to-pin delays as fast as 4.5 ns, and counter speeds of up to 227.3 MHz. MAX 7000A devices in the -4, -5, -6, -7, and some -10 speed grades are compatible with the timing requirements for 33 MHz operation of the PCI Special Interest Group (PCI SIG) PCI Local Bus Specification, Revision 2.2.

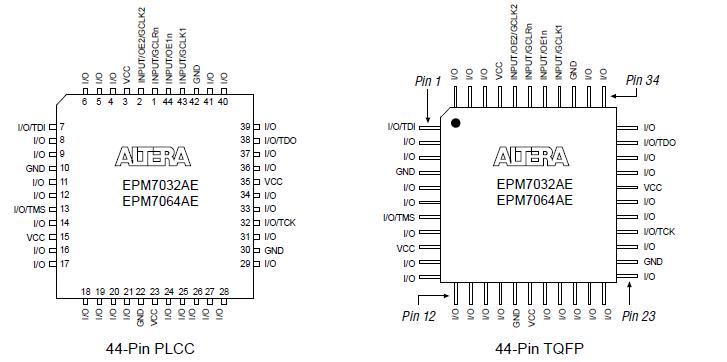

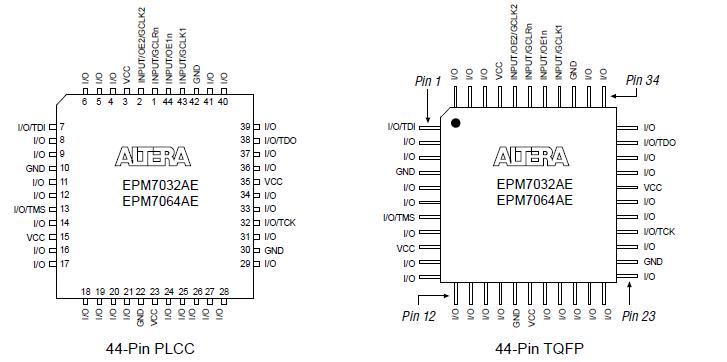

The MAX 7000A architecture supports 100% transistor-to-transistor logic (TTL) emulation and high-density integration of SSI, MSI, and LSI logic functions. It easily integrates multiple devices including PALs, GALs, and 22V10s devices. MAX 7000A devices are available in a wide range of packages, including PLCC, BGA, FineLine BGA, Ultra FineLine BGA, PQFP, and TQFP packages.

MAX 7000A Data Sheet

MAX 7000A Data Sheet