Features: ` 15ps Differential Output-to-Output Skew

` 1.7psRMS Added Random Jitter

` 150ps (max) Part-to-Part Skew

` 450ps Propagation Delay

` Synchronous Output Enable/Disable

` Single-Ended Monitor Output

` Outputs Assert Low when CLK, CLK are Open or at GND

` 3.0V to 3.6V Supply Voltage Range

` -40 to +85 Operating Temperature RangeApplication·Precision Clock Distribution

·Low-Jitter Data Repeater

·Data and Clock Driver and Buffer

·Central-Office Backplane Clock Distribution

·DSLAM Backplane

·Base Station

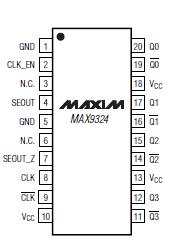

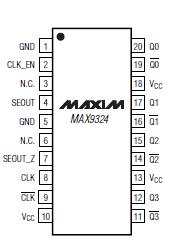

·ATEPinout Specifications

SpecificationsVCC to GND...........................................................-0.3V to +4.0V

Q_, Q_, CLK, CLK, SEOUT_Z, CLK_EN,

SEOUT to GND.............................................-0.3V to (VCC + 0.3V)

CLK to CLK............................................................................±3V

SEOUT Short to GND .................................................Continuous

Continuous Output Current (Q_, Q_) ................................50mA

Surge Output Current (Q_, Q_) .......................................100mA

Continuous Power Dissipation (TA = +70)

20-Pin TSSOP (derate 11mW/)..................................879.1mW

20-Pin 4mm ✕ 4mm Thin QFN (derate 16.9mW/)....1349.1mW

Junction-to-Ambient Thermal Resistance in Still Air

20-Pin TSSOP ...............................................................+91/W

20-Pin 4mm ✕ 4mm Thin QFN....................................+59.3/W

Junction-to-Case Thermal Resistance

20-Pin TSSOP ...............................................................+20/W

20-Pin 4mm ✕ 4mm Thin QFN.........................................+2/W

Operating Temperature Range ...........................-40 to +85

Junction Temperature......................................................+150

Storage Temperature Range .............................-65 to +150

Soldering Temperature (10s) ..........................................+300

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

DescriptionThe MAX9324 low-skew, low-jitter, clock and data driver distributes a differential LVPECL input to four differential LVPECL outputs and one single-ended LVCMOS output.

All outputs default of MAX9324 to logic low when the differential inputs equal GND or are left open. The MAX9324 operates from 3.0V to 3.6V, making it ideal for 3.3V systems, and consumes only 25mA (max) of supply current.

The MAX9324 features low 150ps (max) part-to-part skew, low 15ps output-to-output skew, and low 1.7ps RMS jitter, making the device ideal for clock and data distribution across a backplane or board. CLK_EN and SEOUT_Z control the status of the various outputs.

Asserting CLK_EN low configures the differential (Q_, Q_) outputs to a differential low condition and SEOUT to a single-ended logic-low state. CLK_EN operation of MAX9324 is synchronous with the CLK_ inputs. A logic high on SEOUT_Z places SEOUT in a high-impedance state.

SEOUT_Z is asynchronous with the CLK (CLK) inputs.

The MAX9324 is available in space-saving 20-pin TSSOP and ultra-small 20-pin 4mm ✕ 4mm thin QFN packages and operates over the extended (-40 to +85) temperature range.

MAX9324 Data Sheet

MAX9324 Data Sheet