Features: ·No Reference Clock Required for Data Acquisition

·Input Data Rates: 2.488Gbps or 2.67Gbps

·Fully Integrated Clock and Data Recovery with Limiting Amplifier and 1:4 Demultiplexer

·Parallel Output Rate: 622Mbps/667Mbps

·Differential Input Range: 10mVP-P to 1.6VP-P without Threshold Adjust

·Differential Input Range: 50mVP-P to 600mVP-P with Threshold Adjust

·0.65UI High-Frequency Jitter Tolerance

·Loss-of-Lock (LOL) Indicator

·Wide Input Threshold Adjust Range: ±170mV

·Maintain Valid Clock Output in Absence of Data Transitions

·System Loopback Input Available for System Diagnostic Testing

·Operating Temperature Range -40°C to +85°C

·Low Power Dissipation: 610mW at +3.3VApplication·SDH/SONET Receivers and Regenerators

·Add/Drop Multiplexers

·Digital Cross-Connects

·SDH/SONET Test

·Equipment

·DWDM Transmission

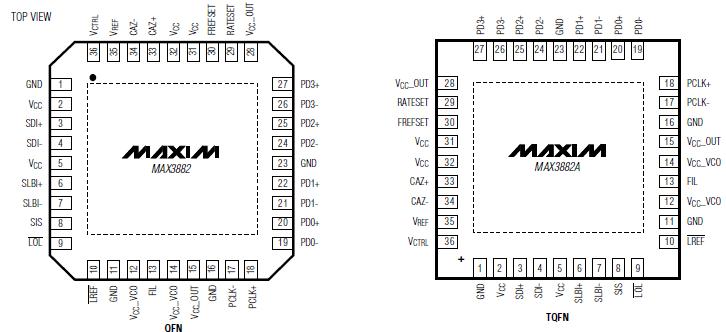

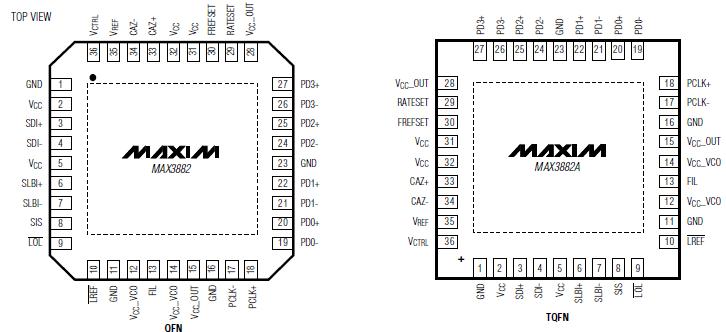

·SystemsPinout Specifications

SpecificationsSupply Voltage, VCC............................................-0.5 to +5.0V

Input Voltage Level

(SDI+, SDI-, SLBI+, SLBI-) ..........(VCC - 1.0V) to (VCC + 0.5V)

Input Current Levels (SDI+, SDI-, SLBI+, SLBI-)..........±20mA

LVDS Output Voltage Levels

(PCLK±, PD_±).....................................-0.5V to (VCC + 0.5V)

Voltage at LOL, RATESET, SIS, LREF, VREF, FIL, CAZ+,

CAZ-, VCTRL, FREFSET ..........................-0.5V to (VCC + 0.5V)

Continuous Power Dissipation (TA = +85°C)

36-Lead QFN (derate 32.4mW/°C above +85°C) ....830mW

Operating Temperature Range ...................-40°C to +85°C

Storage Temperature Range ....................-55°C to +150°C

Lead Temperature (soldering, 10s) ..........................+300°C

DescriptionThe MAX3882A is a deserializer combined with clock and data recovery and limiting amplifier ideal for converting 2.488Gbps/2.67Gbps serial data to 4-bit-wide, 622Mbps/667Mbps parallel data for SDH/SONET applications. The MAX3882A accepts serial NRZ input data as low as 10mVP-P of 2.488Gbps/2.67Gbps and generates four parallel LVDS data outputs at 622Mbps/667Mbps. Included is an additional high-speed serial data input for system loopback diagnostic testing. For data acquisition, the MAX3882A does not require an external reference clock. However, if needed, the loopback input can be connected to an external reference clock of 155MHz/167MHz or 622MHz/667MHz to maintain a valid clock output in the absence of input data transitions. Additionally, a TTL-compatible loss-of-lock output is provided. The device provides a vertical threshold adjustment to compensate for optical noise generated by EDFAs in WDM transmission systems. The MAX3882A operates from a single +3.3V supply and consumes 610mW.

The MAX3882A operates at 2.488Gbps only. The MAX3882's jitter performance exceeds all SDH/ SONET specifications. The device is available in a 6mm * 6mm 36-pin QFN package.

MAX3882A Data Sheet

MAX3882A Data Sheet