Features: · 2.488Gbps and 2.667Gbps Input Data Rates

· Reference Clock Not Required for Data Acquisition

· Exceeds ANSI, ITU, and Bellcore SONET/SDH Jitter Specifications

· 2.7mUIRMS Clock Jitter Generation

· 10mVP-P Input Sensitivity Without Threshold Adjust

· 0.65UIP-P High-Frequency Jitter Tolerance

· ±170mV Wide Input Threshold Adjust Range

· Clock Holdover Capability Using Frequency- Selectable Reference Clock

· Serial Loopback Input Available for System Diagnostic Testing

· Loss-of-Lock (LOL) Indicator

· Small 5mm× 5mm 32-Pin QFN PackageApplication·SONET/SDH Receivers and Regenerators

·Add/Drop Multiplexers

·Digital Cross-Connects

·SONET/SDH Test Equipment

·DWDM Transmission Systems

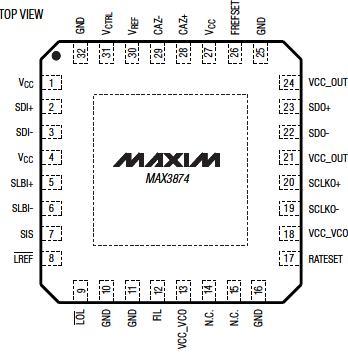

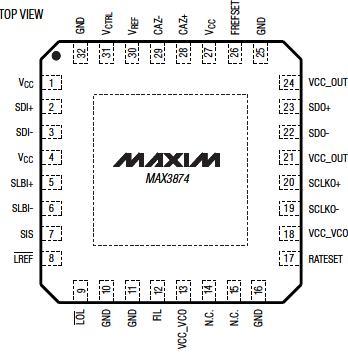

·Access NetworksPinout Specifications

SpecificationsSupply Voltage, VCC...........................................-0.5V to +5.0V

Input Voltage Levels (SDI+, SDI-,

SLBI+, SLBI-) .................................(VCC - 1.0V) to (VCC + 0.5V)

Input Current Levels (SDI+, SDI-, SLBI+, SLBI-)............±20mA

CML Output Current (SDO+, SDO-, SCLKO+, SCLKO-) ...±22mA

Voltage at LOL, LREF, SIS, FIL, RATESET, FREFSET,

VCTRL, VREF, CAZ+, CAZ-..........................-0.5V to (VCC + 0.5V)

Continuous Power Dissipation (TA = +85°C)

32-Pin QFN (derate 21.3mW/°C above +85°C) .........1384mW

Operating Junction Temperature Range........-55°C to +150°C

Storage Temperature Range ........................-55°C to +150°C

Processing Temperature (die) .......................................+400°C

Lead Temperature (soldering, 10s) ...............................+300°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

DescriptionThe MAX3874 is a compact, dual-rate clock and data recovery with limiting amplifier for OC-48 and OC-48 with FEC SONET/SDH applications. Without using an external reference clock, the fully integrated phaselocked loop (PLL) recovers a synchronous clock signal from the serial NRZ data input. The input data of MAX3874 is then retimed by this recovered clock, providing a clean data output. An additional serial input (SLBI±) is available for system-loopback diagnostic testing. Alternatively, this input of MAX3874 can be connected to a reference clock to maintain a valid clock output in the absence of data transitions. The device also includes a loss-of-lock (LOL) output.

The MAX3874 contains a vertical threshold control to compensate for optical noise due to EDFAs in DWDM transmission systems. The recovered data and clock outputs are CML with on-chip 50 back termination on each line. Its jitter performance exceeds all SONET/SDH specifications. The MAX3874A is the MAX3874 with a voltage-controlled oscillator (VCO) centered at 2.0212GHz.

The MAX3874 operates from a single +3.3V supply and typically consumes 580mW. It is available in a 5mm *5mm 32-pin QFN with exposed pad package and operates over the -40°C to +85°C temperature range.

MAX3874 Data Sheet

MAX3874 Data Sheet