Features: ` Low-voltage operation, 3.3-V JEDEC compatible - VCC = +3.0 V to +3.6 V

` < 5 mA standby current

` Patented design allows minimal standby current without speed degradation

` Exclusively designed for 3.3-V applications

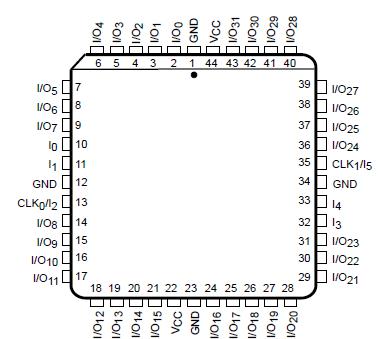

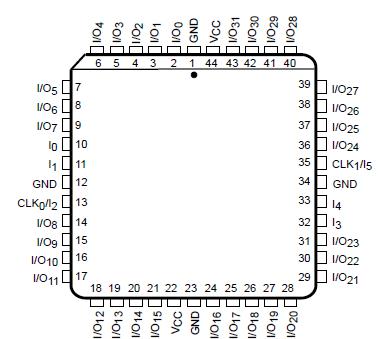

` 44 Pins

` 64 Macrocells

` 12 ns tPD Commercial 18 ns tPD Industrial

` 83.3 MHz fCNT

`38 Bus-Friendly Inputs

` 32 Outputs

` 64 Flip-flops; 2 clock choices

` 4 "PAL22V16" blocks with buried macrocells

` Pin-, function-, and JEDEC-compatible with MACH210

` Pin-compatible with MACH110, MACH111, MACH210, MACH211, and MACH215

Pinout SpecificationsStorage Temperature . . . . . . . . . . . . . . . . . . . . . . . . .65°C to +150°C

SpecificationsStorage Temperature . . . . . . . . . . . . . . . . . . . . . . . . .65°C to +150°C

Ambient Temperature

with Power Applied . . . . . . . . . . . . . . . . . . . . .. . . . . . 55°C to +125°C

Supply Voltage with

Respect to Ground . . . . . . . . . . . . . . . . . . . . . . . . ... . . 0.5 V to +5.0 V

DC Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . .0.5 V to VCC + 0.5 V

DC Output or

I/O Pin Voltage . . . . . . . . . . . . . . . . . . . . . . . . .. . .0.5 V to VCC + 0.5 V

Static Discharge Voltage . . . . . . . . . . . . . . . . . . . . . . .. . .. . . . . . 2001 V

Latchup Current (TA = 0°C to +70°C) . . . . . . . . . . . . . . . . . . . . 200 mA

Stresses above those listed under Absolute Maximum Ratings

may cause permanent device failure. Functionality at or above

these limits is not implied. Exposure to Absolute Maximum

Ratings for extended periods may affect device reliability.

Programming conditions may differDescriptionThe MACHLV210 is a member of the highperformance EE CMOS MACH 2 device family. This device has approximately six times the logic macrocell capability of the popular PAL22V10 at an equal speed with a lower cost per macrocell. It is architecturally identical to the MACH210, with the addition of I/O pull-up/pull-down resistors and low-voltage, low-power operation.

The MACHLV210 provides 3.3-V operation with lowpower CMOS technology. The patented design allows for minimal standby current without speed degradation by limiting the leakage current when signals are not switching. At less than 5 mA maximum standby current, the MACHLV210 is ideal for low-power applications.

The MACHLV210 consists of four PAL blocks interconnected by a programmable switch matrix. The four PAL blocks are essentially "PAL22V16" structures complete with product-term arrays and programmable macrocells, including additional buried macrocells. The switch matrix connects the PAL blocks to each other and to all input pins, providing a high degree of connectivity between the fully-connected PAL blocks. This allows designs to be placed and routed efficiently.

The MACHLV210 has two kinds of macrocell: output and buried. The MACHLV210 output macrocell provides registered, latched, or combinatorial outputs with programmable polarity. If a registered configuration is chosen, the register can be configured as D-type or T-type to help reduce the number of product terms. The register type decision can be made by the designer or by the software. All output macrocells can be connected to an I/O cell. If a buried macrocell is desired, the interna feedback path from the macrocell can be used, which frees up the I/O pin for use as an input.

The MACHLV210 has dedicated buried macrocells which, in addition to the capabilities of the output macrocell, also provide input registers or latches for use in synchronizing signals and reducing setup time requirements.

MACHLV210-15 Data Sheet

MACHLV210-15 Data Sheet