| Item |

Specification |

| No. of channels |

2 (cycle steal method) |

| Transfer memory space |

• From any address in the 1M bytes space to a fixed address

• From a fixed address to any address in the 1M bytes space

• From a fixed address to a fixed address

(Note that DMA-related registers [002016 to 003F16] cannot be accessed) |

| Maximum No. of bytes transferred |

128K bytes (with 16-bit transfers) or 64K bytes (with 8-bit transfers) |

| DMA request factors (Note) |

Falling edge or both edge of pin INT0

Falling edge of pin INT1

Timer A0 to timer A4 interrupt requests

Timer B0 to timer B2 interrupt requests

UART0 transmission and reception interrupt requests

UART2 transmission and reception interrupt requests

Multi-master I2C-BUS interface 0 interrupt request

Multi-master I2C-BUS interface 1 interrupt request

A-D conversion interrupt request

OSD1 and OSD2 interrupt requests

Data slicer interrupt request

VSYNC interrupt request

Software triggers |

| Channel priority |

DMA0 takes precedence if DMA0 and DMA1 requests are generated simultaneously |

| Transfer unit |

8 bits or 16 bits |

| Transfer address direction |

forward/fixed (forward direction cannot be specified for both source and destination simultaneously) |

| Transfer mode |

• Single transfer mode

After the transfer counter underflows, the DMA enable bit turns to "0", and theDMAC turns inactive

• Repeat transfer mode

After the transfer counter underflows, the value of the transfer counter reload register is reloaded to the transfer counter.

The DMAC remains active unless a "0" is written to the DMA enable bit. |

| DMA interrupt request generation timing |

When an underflow occurs in the transfer counter |

| Active |

When the DMA enable bit is set to "1", the DMAC is active.

When the DMAC is active, data transfer starts every time a DMA transfer request signal occurs. |

| Inactive |

• When the DMA enable bit is set to "0", the DMAC is inactive.

• After the transfer counter underflows in single transfer mode |

| Forward address pointer andreload timing for transfer counter |

At the time of starting data transfer immediately after turning the DMAC active,the value of one of source pointer and destination pointer - the one specified for the forward direction - is reloaded to the forward direction address pointer, andthe value of the transfer counter reload register is reloaded to the transfer counter. |

| Writing to register |

Registers specified for forward direction transfer are always write enabled.

Registers specified for fixed address transfer are write-enabled when the DMA enable bit is "0". |

| Reading the register |

Can be read at any time.

However, when the DMA enable bit is "1", reading the register set up as the forward register is the same as reading the value of the forwardaddress pointer. |

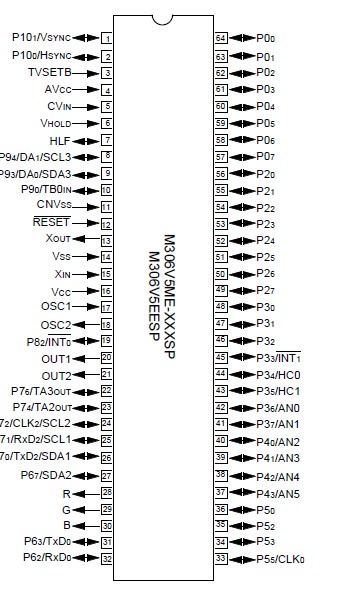

M306V5EESP Data Sheet

M306V5EESP Data Sheet