Features: `SUPPLY VOLTAGE

VDD = 1.65V to 2.2V Core Power Supply

VDDQ= 1.65V to 2.2V for Input/Output

VPP = 12V for fast Program (optional)

`ACCESS TIMES: 90ns, 120ns

`PROGRAMMING TIME

10µs typical

Double Word Programming Option

`COMMON FLASH INTERFACE

64 bit Security Code

`MEMORY BLOCKS

Parameter Blocks (Top or Bottom location)

Main Blocks

`BLOCK LOCKING

All blocks locked at Power Up

Any combination of blocks can be locked

WP for Block Lock-Down

`SECURITY

64 bit user Programmable OTP cells

64 bit unique device identifier

One Parameter Block Permanently Lockable

`AUTOMATIC STAND-BY MODE

`PROGRAM and ERASE SUSPEND

`100,000 PROGRAM/ERASE CYCLES per BLOCK

`ELECTRONIC SIGNATURE

Manufacturer Code: 20h

Top Device Code, M28R400CT: 882Ah

Bottom Device Code, M28R400CB: 882BhPinout Specifications

Specifications

| Symbol |

Parameter |

Value |

Unit |

| Min |

Max |

| TA |

Ambient Operating Temperature (1) |

40 |

85 |

°C |

| TBIAS |

Temperature Under Bias |

40 |

125 |

°C |

| TSTG |

Storage Temperature |

55 |

155 |

°C |

| VIO |

Input or Output Voltage |

0.5 |

VDDQ + 0.5 |

V |

| VDD, VDDQ |

Supply Voltage |

0.5 |

2.7 |

V |

| VPP |

Program Voltage |

0.5 |

13 |

V |

| tVPPH |

Time for VPP at VPPH |

|

100 |

hours |

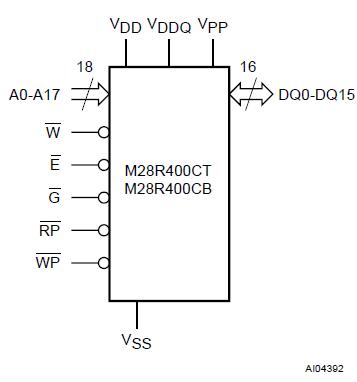

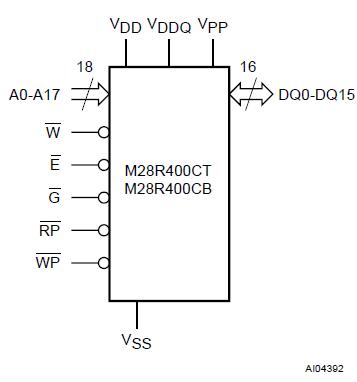

DescriptionThe M28R400C is a 4 Mbit (256Kbit x 16) non-volatile Flash memory that can be erased electrically at the block level and programmed in-system on a Word-by-Word basis. These operations can be performed using a single low voltage (1.65 to 2.2V) supply. VDDQ allows to drive the I/O pin down to 1.65V. An optional 12V VPP power supply is provided to speed up customer programming.

The M28R400C features an asymmetrical blocked architecture. The M28R400C has an array of 15 blocks: 8 Parameter Blocks of 4 KWord and 7 Main Blocks of 32 KWord. M28R400CT has the Parameter Blocks at the top of the memory address space while the M28R400CB locates the Parameter Blocks starting from the bottom. The memory maps are shown in Figure 4, Block Addresses.

The M28R400C features an instant, individual block locking scheme that allows any block to be locked or unlocked with no latency, enabling instant code and data protection. All blocks have three levels of protection. They can be locked and locked-down individually preventing any accidental programming or erasure. There is an additional hardware protection against program and block erase. When VPP £ VPPLK all blocks are protected against program or block erase. All blocks are locked at power-up.

Each block of M28R400C can be erased separately. Erase can be suspended in order to perform either read or program in any other block and then resumed. Program can be suspended to read data in any other block and then resumed. Each block can be programmed and erased over 100,000 cycles.

The M28R400C includes a 128 bit Protection Register and a Security Block to increase the protection of a system design. The Protection Register is divided into two 64 bit segments, the first one contains a unique device number written by ST, while the second one is one-time-programmable by the user. The user programmable segment can be permanently protected. The Security Block, parameter block 0, can be permanently protected by the user. Figure 5, shows the Security Block Memory Map.

Program and Erase commands are written to the Command Interface of the memory. An on-chip Program/Erase Controller takes care of the timings necessary for program and erase operations. The end of a program or erase operation can be detected and any error conditions identified. The command set required to control the memory is consistent with JEDEC standards.

The memory of M28R400C is offered in a TFBGA46 (0.75mm pitch) package and is supplied with all the bits erased (set to '1').

M28R400CB Data Sheet

M28R400CB Data Sheet