Features: ` Compatible with I2C Extended Addressing

` Two-Wire I2C Serial Interface Supports 400kHz Protocol

` Single Supply Voltage:

2.5 to 5.5V for M24128-BW, M24256-BW

1.8 to 5.5V for M24128-BR, M24256-BR

` Hardware Write Control

` BYTE and PAGE WRITE (up to 64 Bytes)

` RANDOM and SEQUENTIAL READ Modes

` Self-Timed Programming Cycle

` Automatic Address Incrementing

` Enhanced ESD/Latch-Up Protection

` More than 1 Million Erase/Write Cycles

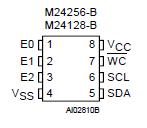

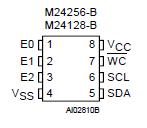

` More than 40-Year Data RetentionPinout Specifications

SpecificationsStressing the device outside the ratings listed in Table 7. may cause permanent damage to the device. These are stress ratings only, and operation of the device at these, or any other conditions outside those indicated in the Operating sections of this specification, is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

|

Symbol |

Parameter |

Min. |

Max. |

Unit |

| TA |

Ambient Operating Temperature |

40 |

125 |

|

| TSTG |

Storage Temperature |

65 |

150 |

|

| TLEAD |

Lead Temperature during Soldering

|

See note 1 |

|

| VIO |

Input or Output range |

0.50 |

6.5 |

V |

| VCC |

Supply Voltage |

0.50 |

6.5 |

V |

| VESD |

Electrostatic Discharge Voltage (Human Body model) 2 |

-3000 |

3000 |

V |

Note: 1. Compliant with JEDEC Std J-STD-020C (for small body, Sn-Pb or Pb assembly), the ST ECOPACK® 7191395 specification, and the European directive on Restrictions on Hazardous Substances (RoHS) 2002/95/EU

2. AEC-Q100-002 (compliant with JEDEC Std JESD22-A114A, C1=100pF, R1=1500, R2=500)DescriptionThese I2C-compatible electrically erasable programmable memory (EEPROM) devices M24256-BR are organized as 32K x 8 bits (M24256-BW and M24256- BR) and 16K x 8 bits (M24128-BW and M24128- BR).

I2C uses a two-wire serial interface, comprising a bi-directional data line and a clock line. The devices carry a built-in 4-bit Device Type Identifier code (1010) in accordance with the I2C bus definition. The device behaves as a slave in the I2C protocol, with all memory operations synchronized by the serial clock. Read and Writeoperations are initiated by a Start condition, generated by the bus mastermaster. The Start condition is followed by a Device Select Code and R ead/Write bit (RW) (as described in Table 3.), terminated by an acknowledge bit.

When writing data to the memory, the M24256-BR inserts an acknowledge bit during the 9th bit time, following the bus master's 8-bit transmission. When data is read by the bus master, the bus master acknowledges the receipt of the data byte in the same way. Data transfers are terminated by a Stop condition after an Ack for Write, and after a NoAck for Read.

Power On Reset

In order to prevent inadvertent Write operations during Power Up, a Power On Reset (POR) circuit is implemented.

At Power Up, the M24256-BR will not respond to any instruction until VCC has reached the POR threshold voltage (this threshold is lower than the VCC minimum operating voltage defined in Table 8. and Table 9.). In the same way, as soon as VCC drops from the normal operating voltage, below the POR threshold voltage, all the operations are disabled and the device will not respond to any instruction. Prior to selecting and issuing instructions to the memory, a valid and stable VCC voltage must be applied. This voltage must remain stable and valid until the end of the transmission of the instruction and, for a Write instruction, until the completion of the internal write cycle (tW).

M24256-BR Data Sheet

M24256-BR Data Sheet