Features: `32-Bit RISC Performance

32-bit ARM® Cortex™-M3 v7M architecture optimized for small-footprint embedded applications

System timer (SysTick), providing a simple, 24-bit clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism

Thumb®-compatible Thumb-2-only instruction set processor core for high code density

50-MHz operation

Hardware-division and single-cycle-multiplication

Integrated Nested Vectored Interrupt Controller (NVIC) providing deterministic interrupt handling

34 interrupts with eight priority levels

Memory protection unit (MPU), providing a privileged mode for protected operating system functionality

Unaligned data access, enabling data to be efficiently packed into memory

Atomic bit manipulation (bit-banding), delivering maximum memory utilization and streamlined peripheral control

`Internal Memory

256 KB single-cycle flash

• User-managed flash block protection on a 2-KB block basis

• User-managed flash data programming

• User-defined and managed flash-protection block

64 KB single-cycle SRAM

`General-Purpose Timers

Four General-Purpose Timer Modules (GPTM), each of which provides two 16-bit timer/counters. Each GPTM can be configured to operate independently as timers or event counters (eight total) as a single 32-bit timer (four total), as one 32-bit Real-Time Clock (RTC) to event capture, or for Pulse Width Modulation (PWM)

32-bit Timer modes

• Programmable one-shot timer

• Programmable periodic timer

• Real-Time Clock when using an external 32.768-KHz clock as the input

• User-enabled stalling in periodic and one-shot mode when the controller asserts the CPU Halt flag during debug

16-bit Timer modes

• General-purpose timer function with an 8-bit prescaler

• Programmable one-shot timer

• Programmable periodic timer

• User-enabled stalling when the controller asserts CPU Halt flag during debug

16-bit Input Capture modes

• Input edge count capture

• Input edge time capture

16-bit PWM mode

• Simple PWM mode with software-programmable output inversion of the PWM signal

`ARM FiRM-compliant Watchdog Timer

32-bit down counter with a programmable load register

Separate watchdog clock with an enable

Programmable interrupt generation logic with interrupt masking

Lock register protection from runaway software

Reset generation logic with an enable/disable

User-enabled stalling when the controller asserts the CPU Halt flag during debug

`10/100 Ethernet Controller

Conforms to the IEEE 802.3-2002 Specification

Full- and half-duplex for both 100 Mbps and 10 Mbps operation

Integrated 10/100 Mbps Transceiver (PHY)

Automatic MDI/MDI-X cross-over correction

Programmable MAC address

Power-saving and power-down modes

`Synchronous Serial Interface (SSI)

Two SSI modules, each with the following features:

Master or slave operation

Programmable clock bit rate and prescale

Separate transmit and receive FIFOs, 16 bits wide, 8 locations deep

Programmable interface operation for Freescale SPI, MICROWIRE, or Texas Instruments synchronous serial interfaces

Programmable data frame size from 4 to 16 bits

Internal loopback test mode for diagnostic/debug testing

`UART

Three fully programmable 16C550-type UARTs with IrDA support

Separate 16x8 transmit (TX) and 16x12 receive (RX) FIFOs to reduce CPU interrupt service loading

Programmable baud-rate generator with fractional divider

Programmable FIFO length, including 1-byte deep operation providing conventional double-buffered interface

FIFO trigger levels of 1/8, ¼, ½, ¾, and 7/8

Standard asynchronous communication bits for start, stop, and parity

False-start-bit detection

Line-break generation and detection

`Analog Comparators

Three independent integrated analog comparators

Configurable for output to: drive an output pin or generate an interrupt

Compare external pin input to external pin input or to internal programmable voltage reference

`I2C

Master and slave receive and transmit operation with transmission speed up to 100 Kbps in Standard mode and 400 Kbps in Fast mode

Interrupt generation

Master with arbitration and clock synchronization, multimaster support, and 7-bit addressing mode

`PWM

Three PWM generator blocks, each with one 16-bit counter, two comparators, a PWM generator, and a dead-band generator

One 16-bit counter

• Runs in Down or Up/Down mode

• Output frequency controlled by a 16-bit load value

• Load value updates can be synchronized

• Produces output signals at zero and load value

Two PWM comparators

• Comparator value updates can be synchronized

• Produces output signals on match

PWM generator

• Output PWM signal is constructed based on actions taken as a result of the counter and PWM comparator output signals

• Produces two independent PWM signals

Dead-band generator

• Produces two PWM signals with programmable dead-band delays suitable for driving a half-H bridge

• Can be bypassed, leaving input PWM signals unmodified

Flexible output control block with PWM output enable of each PWM signal

• PWM output enable of each PWM signal

• Optional output inversion of each PWM signal (polarity control)

• Optional fault handling for each PWM signal

• Synchronization of timers in the PWM generator blocks

• Synchronization of timer/comparator updates across the PWM generator blocks

• Interrupt status summary of the PWM generator blocks

`QEI

Hardware position integrator tracks the encoder position

Velocity capture using built-in timer

Interrupt generation on index pulse, velocity-timer expiration, direction change, and quadrature error detection

`GPIOs

1-46 GPIOs, depending on configuration

5-V-tolerant input/outputs

Programmable interrupt generation as either edge-triggered or level-sensitive

Bit masking in both read and write operations through address lines

Programmable control for GPIO pad configuration:

• Weak pull-up or pull-down resistors

• 2-mA, 4-mA, and 8-mA pad drive

• Slew rate control for the 8-mA drive

• Open drain enables

• Digital input enables

`Power

On-chip Low Drop-Out (LDO) voltage regulator, with programmable output user-adjustable from 2.25 V to 2.75 V

Hibernation module handles the power-up/down 3.3 V sequencing and control for the core digital logic and analog circuits

Low-power options on controller: Sleep and Deep-sleep modes

Low-power options for peripherals: software controls shutdown of individual peripherals

User-enabled LDO unregulated voltage detection and automatic reset

3.3-V supply brown-out detection and reporting via interrupt or reset

`Flexible Reset Sources

Power-on reset (POR)

Reset pin assertion

Brown-out (BOR) detector alerts to system power drops

Software reset

Watchdog timer reset

Internal low drop-out (LDO) regulator output goes unregulated

`Additional Features

Six reset sources

Programmable clock source control

Clock gating to individual peripherals for power savings

IEEE 1149.1-1990 compliant Test Access Port (TAP) controller

Debug access via JTAG and Serial Wire interfaces

Full JTAG boundary scan

`Industrial-range 100-pin RoHS-compliant LQFP packageApplication· Remote monitoring

· Electronic point-of-sale (POS) machines

· Test and measurement equipment

· Network appliances and switches

· Factory automation

· HVAC and building control

· Gaming equipment

· Motion control

· Medical instrumentation

· Fire and security

· Power and energy

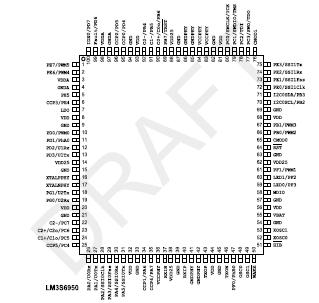

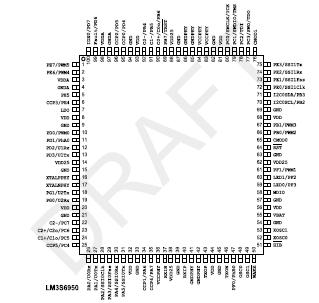

· TransportationPinout Specifications

SpecificationsThe maximum ratings are the limits to which the device can be subjected without permanently damaging the device.

Note: The device is not guaranteed to operate properly at the maximum ratings.

Characteristic

a |

Symbol |

Value |

Unit |

|

Min |

Max |

| I/O supply voltage (VDD) |

VDD |

0 |

4 |

V |

| Core supply voltage (VDD25) |

VDD25 |

0 |

4 |

V |

| Analog supply voltage (VDDA) |

VDDA |

0 |

4 |

V |

| Battery supply voltage (VBAT) |

VBAT |

0 |

4 |

V |

| Ethernet PHY supply voltage (VCCPHY) |

VCCPHY |

0 |

4 |

V |

| Input voltage |

VIN |

-0.3 |

5.5 |

V |

| Maximum current per output pins |

I |

- |

25 |

mA |

a. Voltages are measured with respect to GND.

Important: This device contains circuitry to protect the inputs against damage due to high-static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (for example, either GND or VDD).

DescriptionThe Luminary Micro Stellaris® family of microcontrollers-the first ARM® Cortex™-M3 based controllers-brings high-performance 32-bit computing to cost-sensitive embedded microcontroller applications. These pioneering parts deliver customers 32-bit performance at a cost equivalent to legacy 8- and 16-bit devices, all in a package with a small footprint.

The Stellaris® family offers efficient performance and extensive integration, favorably positioning the device into cost-conscious applications requiring significant control-processing and connectivity capabilities. The Stellaris® LM3S2000 series, designed for Controller Area Network (CAN) applications, extends the Stellaris family with Bosch CAN networking technology, the golden standard in short-haul industrial networks. The Stellaris® LM3S2000 series also marks the first integration of CAN capabilities with the revolutionary Cortex-M3 core. The Stellaris® LM3S60 00 series combines both a 10/100 Ethernet Media Access Control (MAC) and Physical (PHY) layer, marking the first time that integrated connectivity is available with an ARM Cortex-M3 MCU and the only integrated 10/100 Ethernet MAC and PHY available in an ARM architecture MCU.

The LM3S6950 microcontroller is targeted for industrial applications, including remote monitoring,electronic point-of-sale machines, test and measurement equipment, network appliances and switches, factory automation, HVAC and building control, gaming equipment, motion control, medical instrumentation, and fire and security.

For applications requiring extreme conservation of power, the LM3S6950 microcontroller features a Battery-backed Hibernation module to efficiently power down the LM3S6950 to a low-power state during extended periods of inactivity. With a power-up/power-down sequencer, a continuous time counter (RTC), a pair of match registers, an APB interface to the system bus, and dedicated non-volatile memory, the Hibernation module positions the LM3S6950 microcontroller perfectly for battery applications.

In addition, the LM3S6950 microcontroller offers the advantages of ARM's widely available development tools, System-on-Chip (SoC) infrastructure IP applications, and a large user community. Additionally, the microcontroller uses ARM's Thumb®-compatible Thumb-2 instruction set to reduce memory requirements and, thereby, cost. Finally, the LM3S6950 microcontroller is code-compatible to all members of the extensive Stellaris® family; providing flexibility to fit our customers' precise needs.

Luminary Micro offers a complete solution to get to market quickly, with evaluation and development boards, white papers and application notes, an easy-to-use peripheral driver library, and a strong support, sales, and distributor network.

LM3S6950 Data Sheet

LM3S6950 Data Sheet