Features: ` Fast Cycle Times: 20/25/30 ns

` Selectable 36/18/9-Bit Word Width for Both Input Port and Output Port

` Byte-Order-Reversal Function (i.e., 'Big-Endian' 'Little-Endian' Conversion)

'Little-Endian' Conversion)

` 16-mA-IOL Three-State Outputs

` Automatic Byte Parity Checking

` Selectable Byte Parity Generation

` Five Status Flags: Full, Almost-Full, Half-Full, Almost-Empty, and Empty

` All FIFO Status Flags are Synchronous (AE, HF, AF Through Programming of Control Register)

` Programmed Values may be entered from either Port

` Two Enable Control Signals for each Port

` Mailbox Register with Synchronized Flags

` Asynchronous Data-Bypass Function

` 'Smart' Data-Retransmit Function

` Configurable for Paralleled FIFO Operation (72-Bit Data Width)

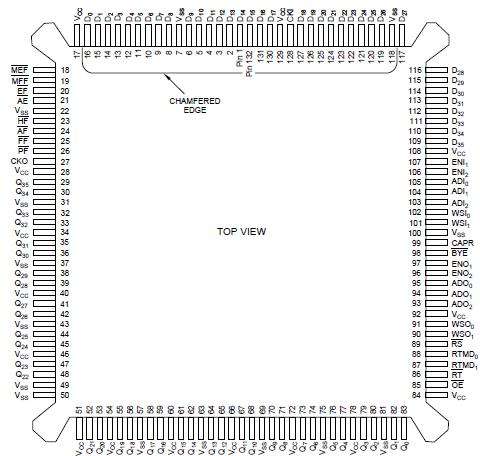

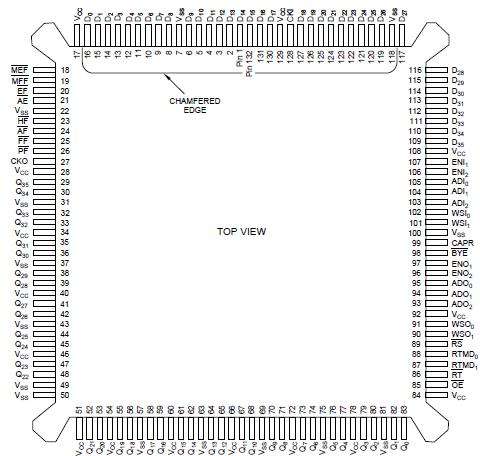

` Space-Saving PQFP and TQFP 1 Packages

` PQFP-to-PGA Package Conversion 2 Pinout Specifications

Specifications

| PARAMETER |

RATING |

| Supply Voltage to VSS Potential |

0.5 V to 7 V |

| Signal Pin Voltage to VSS Potential 2 |

0.5 V to VCC + 0.5 V |

| DC Output Current 3 |

± 75 mA |

| Storage Temperature Range |

65 to 150 |

| Power Dissipation (Package Limit) |

2.5 Watts (Quad Flat Pack) |

NOTES:

1. Stresses greater than those listed under 'Absolute Maximum Ratings' may cause permanent damage to the device. This is a stress rating for transient conditions only. Functional operation of the device at these or any other conditions outside those indicated in the 'Operating Range' of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. Negative undershoot of 1.5 V in amplitude is permitted for up to 10 ns, once per cycle.

3. Outputs should not be shorted for more than 30 seconds. No more than one output should be shorted at any time.

DescriptionThe LH543620 is a FIFO (First-In, First-Out) memory device, based on fully-static CMOS RAM technology, capable of containing up to 1024 36-bit words. It can replace four or more nine-bit-wide FIFOs in many applications.

The input port and the output port operate independently of each other. Write operations are performed on the rising edge of the input clock CKI, and enabled by two enabled signals ENI1, ENI2. Read operations are performed on the rising edge of the output clock CKO and enabled by two enabled signals ENO1, ENO2.

Five status flags are available to monitor the memory array status: Full, Almost-Full, Half-Full, Almost-Empty, and Empty. The Almost-Full and Almost-Empty flags are initialized to a default offset of eight locations from their respective boundaries, but they are each programmable over the entire FIFO depth.

Both the input port and the output port may be set independently to operate at three data-word widths: 36 bits, 18 bits, or 9 bits. This setting may be changed during system operation. The LH543620 can perform Byte-Order- Reversal on the four nine-bit bytes of each 36-bit data word passing through it, thus accomplishing 'Big Endian' 'Little Endian' conversion.

'Little Endian' conversion.

When data is read out of the FIFO a byte-parity check is performed. The parity flag is used to indicate that a parity error was detected in one of the 9-bit bytes of the output word.

Parity generation, when selected, creates the parity bit of each 8-bit byte of the input word. The result is written into the MSB-bit of each 9-bit byte, overwriting the previous contents of the bit. The default is odd parity. However, the FIFO may be programmed to use even parity.

The LH543620 has a data-bypass mode that connects the output port to the input port asynchronously. A mailbox facility with Synchronized Flags is provided from the input port to the output port.

The LH543620's 'Smart-Retransmit' capability sets the internal-memory read pointer to any arbitrary memory location. The 'Smart-Retransmit' capability includes a Marking Function and a Programmable Offset to support data communication and digital signal processing applications.

LH543620 Data Sheet

LH543620 Data Sheet

'Little-Endian' Conversion)

'Little-Endian' Conversion)

'Little Endian' conversion.

'Little Endian' conversion.