Features: ` Integrated clock recovery and data retiming

` Surface-mount package

` Single ECL supply

` Robust FPLL design

` Operation up to BER = 1e3

`SONET/SDH compatible loss of signal alarm

` High effective Q allows long run lengths

` Jitter tolerance exceeding ITU-T/Bellcore

` Low clock jitter generation: typical <0.005 UI

` Standard and custom data rates 0.50 Gbits/s-5.5 Gbits/s

` Complementary 50 I/Os

Application·SONET/SDH receiver terminals and regenerators OC-12 through OC-96/STM-4 through STM-32

· SONET/SDH test equipment

· Proprietary bit rate systems

· Digital video transmission

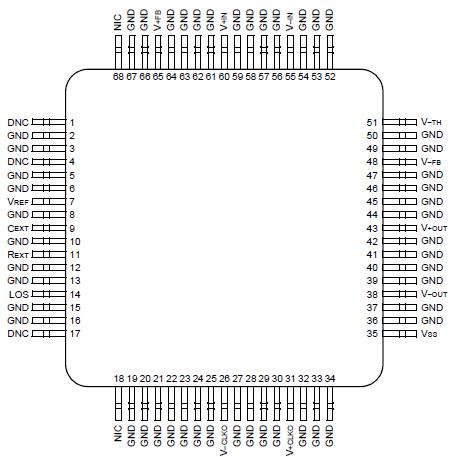

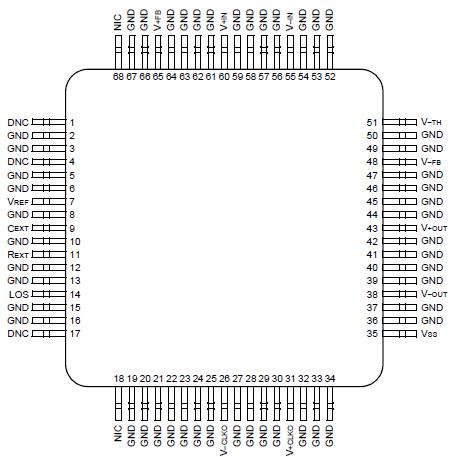

· Clock doublers and quadruplersPinout Specifications

SpecificationsStresses in excess of the absolute maximum ratings can cause permanent or latent damage to the device. These

are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in

excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for

extended periods can adversely affect device reliability.

| Parameter |

Min |

Max |

Unit |

| Supply Voltage Range (VSS) |

-7 |

0.5 |

V |

| Supply Voltage Range (VSS) |

- |

7 |

V |

| Power Dissipation |

- |

2 |

W |

| Voltage (all pins) |

VSS |

0.5 |

V |

| Transient Voltage to ac Couple Pins (V±IN, REXT) |

- |

±3 |

V |

| Storage Temperature Range |

-40 |

125 |

|

| Operating Temperature Range |

-40 |

100 |

|

DescriptionThe LG1600FXH Clock and Data Regenerator (CDR) is a compact, single device solution to clock recovery and data retiming in high-speed communication systems such as fiber-optic data links and long-span fiberoptic regenerators and terminals. Using frequency and phase-lock loop (FPLL) techniques, the device regenerates clean clock and error-free data signals from a nonreturn-to-zero (NRZ) data input, corrupted by jitter and intersymbol interference. The LG1600FXH exceeds ITU-T/Bellcore jitter tolerance requirements for SONET/SDH systems.

The device houses two integrated circuits on an alumina substrate inside a hermetically sealed 3 cm *3 cm (1.2 in. *1.2 in.) surface-mount package: a GaAs IC that contains the high-speed part of an FPLL as well as a highly sensitive decision circuit; and a silicon bipolar IC that contains a loop filter, acquisition, and signal detect circuitry.

The two ac-coupled complementary data inputs can be driven differentially as well as single ended. A dc feedback

voltage VFB maintains a data input threshold VTH (decision level) that is optimum for a wide range of 50% duty cycle input levels (connect to VTH). If needed, the user can supply an external threshold to compensate for different mark densities or distorted input signals (see Figure 10).

Regenerated clock and data are available from complementary outputs that can either be ac coupled, to provide

50 output match, or dc coupled with 50 to ground at the receiving end.

The second-order PLL filter bandwidth is set by the user with an external resistor between pin 11 and ground (required). An internal capacitor provides sufficient PLL damping for most applications. In critical applications, PLL damping can be increased using an external capacitor between pins 9 and 11.

The device is powered by a single 5.2 V ECL compatible supply and typically consumes 1.5 W.

The LG1600FXH comes in standard bit rates, but can be factory tuned for any rate between 500 Mbits/s and

5500 Mbits/s.

A test fixture (TF1004A) with SMA connectors is available to allow quick evaluation of the LG1600FXH.

LG1600FXH Data Sheet

LG1600FXH Data Sheet