Features: Dual Speed CSMA/CD Engine (10 Mbps and 100 Mbps)

Compliant with IEEE 802.3 100BASE-TSpecification

Supports 100BASE-TX, 100BASE-T4, and10BASE-T Physical Interfaces

32 Bit Wide Data Path (into Packet Buffer Memory)

Support for 32 and 16 Bit Buses

Support for 32, 16 and 8 Bit CPU Accesses

Synchronous, Asynchronous and Burst DMA Interface Mode Options

128 Kbyte External Memory

Built-in Transparent Arbitration for Slave Sequential Access Architecture

Early TX, Early RX Functions

Flat MMU Architecture with Symmetric Transmit and Receive Structures and Queues

MII (Media Independent Interface) Compliant MACPHY Interface Running at Nibble Rate

MII Management Serial Interface

Seven Wire Interface to 10 Mbps ENDEC

EEPROM-Based Setup

Full Duplex Capability

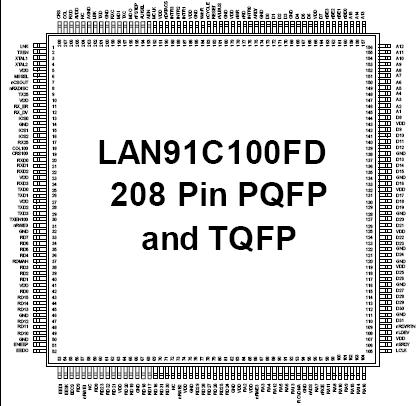

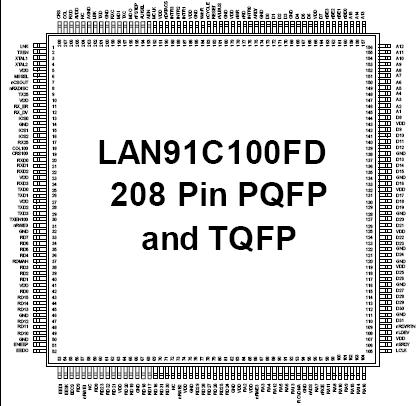

Pinout SpecificationsOperating Temperature Range ........................................................... 0 EC to +70EC

SpecificationsOperating Temperature Range ........................................................... 0 EC to +70EC

Storage Temperature Range ........................................................-55EC°to + 150EC

Lead Temperature Range (soldering, 10 seconds) ........................................ +325EC

Positive Voltage on any pin, with respect to Ground .................................VCC + 0.3V

Negative Voltage on any pin, with respect to Ground ........................................ -0.3V

Maximum VCC ....................................................................................................... +7V

*Stresses above those listed above could cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other condition above those indicated in the operation sections of this specification is not implied.

Note: When powering this device from laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes on their outputs when the AC power is switched on or off. In addition, voltage transients on the AC power line may appear on the DC output. If this possibility exists, it is suggested that a clamp circuit be used.DescriptionThe LAN91C100FD is designed to facilitate the implementation of first generation Fast Ethernet adapters and connectivity

products. For this first generation of products, flexibility dominates over integration. The LAN91C100FD is a digital device that implements the MAC portion of the CSMA/CD protocol at 10 and 100 Mbps, and couples it with a lean and fast data and control path system architecture to ensure the CPU to packet RAM data movement does not cause a bottleneck at 100 Mbps.

Total memory size is 128 Kbytes, equivalent to a total chip storage (transmit plus receive) of 64 outstanding packets. The LAN91C100FD is software compatible with the LAN9000 family of products and can use existing LAN9000 drivers (ODI, IPX, and NDIS) in 16 and 32 bit Intel X86 based environments.

Memory management is handled using a unique MMU (Memory Management Unit) architecture and a 32-bit wide data path. This I/O mapped architecture can sustain back-to-back frame transmission and reception for superior data throughput and optimal performance. It also dynamically allocates buffer memory in an efficient buffer utilization scheme, reducing software tasks and relieving the host CPU from performing these housekeeping functions. The total memory size is 128 Kbytes (external), equivalent to a total chip storage (transmit and receive) of 64 outstanding packets.

FEAST provides a flexible slave interface for easy connectivity with industry-standard buses. The Bus Interface Unit (BIU) can handle synchronous as well as asynchronous buses, with different signals being used for each one. FEAST's bus interface supports synchronous buses like the VESA local bus, as well as burst mode DMA for EISA environments. Asynchronous bus support for ISA is supported even though ISA cannot sustain 100 Mbps traffic. Fast Ethernet could be adopted for ISA-based nodes on the basis of the aggregate traffic benefits.

Two different interfaces are supported on the network side. The first is a conventional seven wire ENDEC interface that connects to the LAN83C694 for 10BASE-T and coax 10 Mbps Ethernet networks. The second interface follows the MII (Media Independent Interface) specification draft standard, consisting of 4 bit wide data transfers at the nibble rate. This interface is applicable to 10 Mbps or 100 Mbps networks. Three of the LAN91C100FD's pins are used to interface to the two-line MII serial management protocol. Four I/O ports (one input and three output pins) are provided for LAN83C694 configuration.

The LAN91C100FD is based on the LAN91C100 FEAST, functional revision G modified to add full duplex capability. Also added is a software-controlled option to allow collisions to discard receive packets. Previously, the LAN91C100 supported a "Diagnostic Full Duplex" mode. Under this mode the transmit packet is looped internally and received by the MAC. This mode was enabled using the FDUPLX bit in the TCR. In order to avoid confusion, the new, broader full duplex function of the LAN91C100FD is designated as Switched Full Duplex, and the TCR bit enabling it is designated as SWFDUP. When the LAN91C100FD is configured for SWFDUP, its transmit and receive paths will operate independently and some CSMA/CD functions will be disabled. When the controller is not configured for SWFDUP it will follow the CSMA/CD protocol.

LAN91C100FD Data Sheet

LAN91C100FD Data Sheet