Features: Single chip supports an 8 x 8 port switch at 155Mbps per

port

Central Memory Architecture eliminates Head-of-Line

Blocking by sharing the memory array with all ports

Low power dissipation

- 330mW (typ.)

Data Path Interface (DPI) provides configurable Input and

Output ports; up to 8 receive and 8 transmit ports at

155Mbps

Supports data rates up to 1.2Gbps with a 32-bit wide port

configuration; 155Mbps per 4-bit port

Can be cascaded for larger switch configurations

Fast Input/Output port cycle times

Expander and Concentrator function is fully supported by

the Input and Output port configuration options

8192 cells (52 to 56 bytes each) of on-chip buffer memory

capacity

Configurable cell lengths of 52, 53, 54, 55, or 56 bytes can

be independently chosen for Input and Output ports

Byte Addition or Byte Subtraction for x4/x8 to x16/x32

conversion capability

Internal header Cyclical Redundancy Check (CRC) and

generation logic on-chip

Header modification, pre-pend, and post-pend operations

available as well as Multicasting and Broadcasting

capability

High-bandwidth control port for queue controller system

block, up to 36 MHz cycle time

Can be used with the companion IDT77V500 Switch

Controller or custom logic for traffic management

Industrial temperature range (-40°C to +85°C) is available

Single +3.3V ± 300mV power supply

Available in an 208-pin Plastic Quad Flat Pack (PQFP) and

256-ball BGA

Pinout Specifications

Specifications

| Symbol |

Rating1

|

Commercial |

Unit |

| VTERM2 |

Terminal Voltage with Respect to VSS |

−0.5 to +3.9 |

V |

| TBIAS |

Temperature Under Bias |

−55 to +125 |

|

| TSTG |

Storage Temperature |

−55 to +125 |

|

| IOUT |

DC Output Current |

50 |

mA |

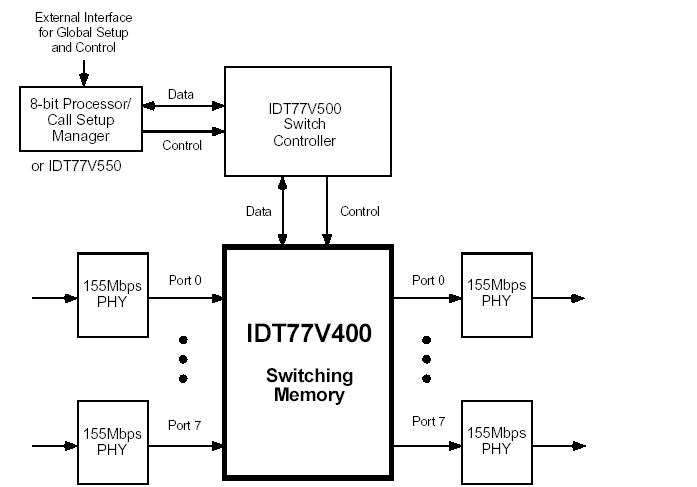

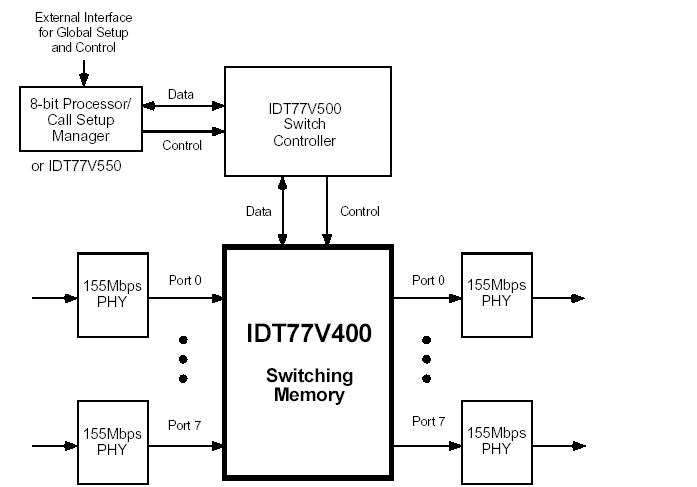

DescriptionThe IDT77V400 ATM Cell Based Switching Memory provides the logic and memory necessary to perform high-speed buffering and switching operations on ATM cell data. A single IDT77V400 provides a cost effective switching element to implement an 8 x 8 155Mbps switch with 1.2Gbps total switching bandwidth. The user of IDT77V400 configurable data ports provide an aggregate bandwidth of 1.2Gbps for both receive and transmit functions, and the cell lengths are user programmable to up to 56 bytes.

The memory provides storage for 8192 ATM cells, each of which can be as large as 56-bytes in length. The main cell of IDT77V400 memory is implemented as a Buffer Memory array, and an on-chip cell address counter keeps track of cell refresh requirements. There are also sixteen double-buff- ered Serial Access Memories (SAM); eight for receiving and eight for transmitting the ATM cells.

The input data ports and output data ports are configurable from eight ports of 4-bits at 155Mbps each up to one 32-bit wide port at 1.2Gbps. The sixteen data ports are asynchronous with respect to each other, and each port provides an independent data clock and cell framing signal for start of cell indication. The SAMs IDT77V400 are double-buffered for each input and each output port of IDT77V400 to allow one cell to be transferred to or from the internal memory while that data port continues to receive or transmit a second cell. The cell framing of IDT77V400 and data clock signals imple- ment a simple handshaking and synchronization protocol which allows multiple Switching Memories to be connected to construct larger switch arrays without requiring additional hardware.

IDT77V400 Data Sheet

IDT77V400 Data Sheet