Features: ♦ Data transfers on fixed cell sizes

♦ Programmable cell size

♦ One input port to four output ports

♦ Four Independent output 128 x 9 FIFO Queues

♦ Selectable eighteen bit or nine bit input bus

♦ Selectable eight/nine bit or four bit output buses

♦ Programmable chip Identification

♦ "UtopiaTx" level 2 compliant input interface signaling

♦ "UtopiaTx" level 1 compliant output interface signaling

♦ Separate clocks for input and output

♦ Selectable In-band or Out-band routing

♦ Multicast capability

♦ Data clock rates to 62.5 MHz, 10ns access time

♦ Building Block Implementation allows up to 32 output channels with

a 18, 36 or 64-bit input bus

♦ Four 562 Mbps output channels can be derived from a single

1.1256 Gbps input channel with no additional glue logic

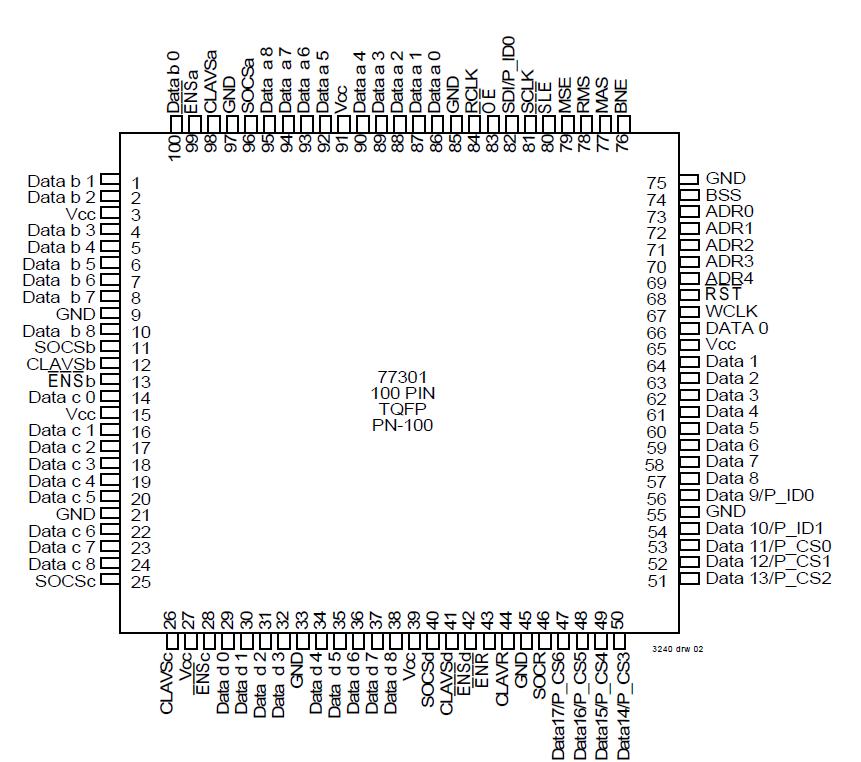

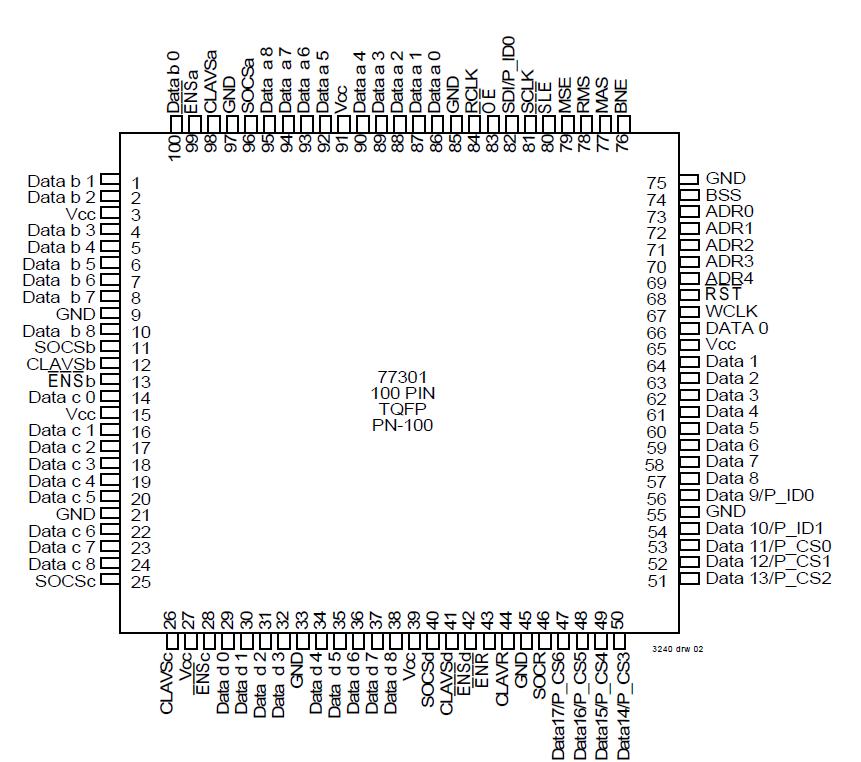

♦ 100-pin TQPF packagePinout Specifications

Specifications

|

Symbol |

Rating |

Commercial |

Industrial |

Unit |

|

VTERM |

Terminal Voltage with Respect to GND |

0.5 to +7.0 |

0.5 to +7.0 |

V |

|

TA |

Operating Temperature |

0 to +70 |

40 to +85 |

C |

|

T-BIAS |

Temperature Under Bias |

55 to +155 |

55 to +155 |

C |

|

T-STG |

Storage Temperature |

55 to +155 |

55 to +150 |

C |

|

IOUT |

DC Output Current |

50 |

50 |

mA |

DescriptionThe IDT77301 UtopiaFIFO is a high-speed, low power single input port supplying four demultiplexing FIFO output ports. Each of the four output synchronous (clocked) FIFOs are 64 words (128 bytes) in depth. Data is written to the input port in "cells" (fixed length data packets). The cell size is programmable from 16 bytes to 128 bytes.

The input port can be configured to support 9-bit or 18-bit wide data buses. (Multiple 77301's can be configured to handle 32 and 64-bit buses with no additional logic.)

There are four routing methods that can be used to transfer data to the 77301. Two methods use out-band routing for the port selection, which requires use of the Address Location bus. The remaining two methods support in-band routing, which uses the Address Location bus in conjunction with the Data bus for port selection. Utopia 2 signaling supports single cell transfers to single output ports, but the IDT77301 also offers a proprietary multicasting protocol. Multicasting enables a single cell to be transferred simultaneously to multiple selected output ports.

The four output ports can be configured as 9-bit or 4-bit wide data buses. (18-bit wide buses can be supported with multiple 77301's with no additional logic required.) Utopia 1 signalling protocol is supported for these ports. Data can be read from each FIFO output port independently.of IDT77301

Separate input and output port clocks are provided and can be operated up to 62.5 MHz. IDT77301 provides the user with 1.125Gbps composite bandwidth on the input port and 562Mbps bandwidth on each output port.

Each 77301 has a unique programmable chip identification register. Multiple UtopiaFIFOs with programmed chip identification can be utilized to direct a 9, 18, 36 or 64-bit bus to as many as 31 output ports.

The principle application for theIDT77301 is in ATM networking based systems, but can be used in any cell based data or telecommunications application requiring the separation of independent data streams from a single input channel.

IDT77301 Data Sheet

IDT77301 Data Sheet