Features: * 0.5 MICRON CMOS Technology

* Typical tSK(o) (Output Skew) < 250ps

* ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200pF, R = 0)

*VCC = 3.3V ± 0.3V, Normal Range

*VCC = 2.7V to 3.6V, Extended Range

*VCC = 2.5V ± 0.2V

* CMOS power levels (0.4 W typ. static)

* Rail-to-Rail output swing for increased noise margin

* Available in SSOP and TSSOP packagesApplication* 3.3V high speed systems

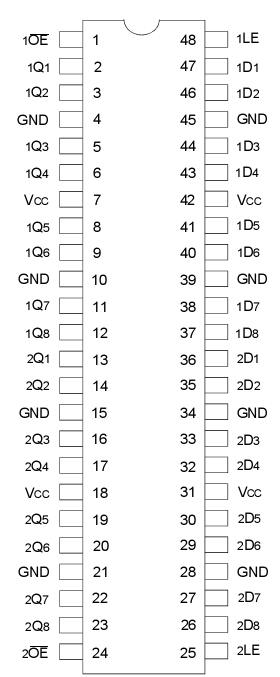

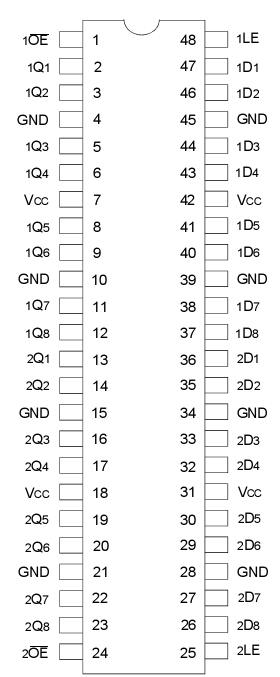

* 3.3V and lower voltage computing systemsPinout Specifications

Specifications

| Symbol |

Description |

Max |

Unit |

VTERM(2)

|

Terminal Voltage with Respect to GND |

0.5 to +4.6 |

V |

VTERM(3)

|

Terminal Voltage with Respect to GND |

0.5 to VCC+0.5 |

V |

| TSTG |

Storage Temperature |

65 to +150 |

°C |

| IOUT |

DC Output Current |

50 to +50 |

mA |

| IIK |

Continuous Clamp Current,

VI < 0 or VI > VCC |

±50 |

mA |

| IOK |

Continuous Clamp Current, VO < 0 |

50 |

mA |

ICC

ISS |

Continuous Current through each

VCC or GND |

±100 |

mA |

DescriptionThis 16-bit transparent D-type latch of the IDT74ALVCH16373 is built using advanced dual metal CMOS technology. The ALVCH16373 is particularly suitable for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers. This device can be used as two 8-bit latches or one 16-bit latch. When the latch enable (LE) input is high, the Q outputs follow the data (D) inputs. When LE is taken low, the Q outputs are latched at the levels set up at the D inputs.

A buffered output-enable (OE) of the IDT74ALVCH16373 can be used to place the eight outputs in either a normal logic state (high or low logic levels) or a high-impedance state. In the

high-impedance state, the outputs neither load nor drive the bus lines signifi- cantly. The high-impedance state and the increased drive provide the capability

to drive bus lines without need for interface or pullup components. OE does not affect internal operations of the latch. Old data can be retained or new data can be enetered while the outputs are in the high-impedance state.

The IDT74ALVCH16373 has been designed with a ±24mA output driver. This driver is capable of driving a moderate to heavy load while maintaining speed performance.

The IDT74ALVCH16373 has "bus-hold" which retains the inputs' last state whenever the input goes to a high impedance. This prevents floating inputs and eliminates the need for pull-up/down resistor.

IDT74ALVCH16373 Data Sheet

IDT74ALVCH16373 Data Sheet