Features: • 0.5 MICRON CMOS Technology

• Typical tSK(o) (Output Skew) < 250ps

• ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200pF, R = 0)

• VCC = 3.3V ± 0.3V, Normal Range

• VCC = 2.7V to 3.6V, Extended Range

• VCC = 2.5V ± 0.2V

• CMOS power levels (0.4 W typ. static)

• Rail-to-Rail output swing for increased noise margin

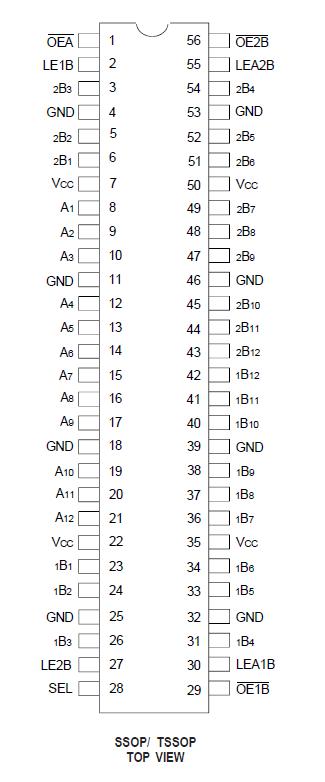

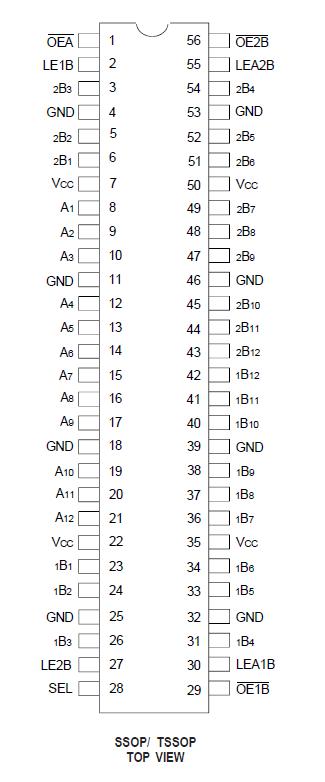

• Available in SSOP and TSSOP packagesApplication• 3.3V high speed systems

• 3.3V and lower voltage computing systemsPinout Specifications

Specifications

| Symbol |

Description |

Max |

Unit |

| VTERM(2) |

Terminal Voltage with Respect to GND |

0.5 to +4.6 |

V |

| VTERM(3) |

Terminal Voltage with Respect to GND |

0.5 to VCC+0.5 |

V |

| TSTG |

Storage Temperature |

65 to +150 |

°C |

| IOUT |

DC Output Curre |

50 to +50 |

mA |

| IIK |

Continuous Clamp Current, |

±50 mA

VI < 0 or VI > |

VC |

| IOK |

Continuous Clamp Current, VO < 0 |

50 |

mA |

|

ICC

ISS |

Continuous Current through each

VCC or GND |

±100 |

mA |

DescriptionThis 12-bit to 24-bit multiplexed D-type latch of the IDT74ALVCH16260 is built using advanced dual metal CMOS technology. The ALVCH16260 is used in applications in which two separate data paths must be multiplexed onto, or demultiplexed from, a single data path. Typical applications include multiplexing and/or demultiplexing address and data information in microprocessor or bus-interface applications. This device also is useful in memory interleaving applications.

Three 12-bit I/O ports (A1-A12, 1B1-1B12, and 2B1-2B12) of the IDT74ALVCH16260 are available for address and/or data transfer. The output-enable (OE1B, OE2B, and OEA) inputs control the bus transceiver functions. The OE1B and OE2B control signals also allow bank control in the A-to-B direction. Address and/or data information can be stored using the internal storage latches. The latch-enable (LE1B, LE2B, LEA1B, and LEA2B) inputs are used to control data storage. When the latch-enable input is high, the latch is transparent. When the latchenable input goes low, the data present at the inputs is latched and remains latched until the latch-enable input is returned high.

The IDT74ALVCH16260 has been designed with a ±24mA output driver. This driver is capable of driving a moderate to heavy load while maintaining speed performance.

The IDT74ALVCH16260 has "bus-hold" which retains the inputs' last state whenever the input goes to a high impedance. This prevents floating inputs and eliminates the need for pull-up/down resistors.

IDT74ALVCH16260 Data Sheet

IDT74ALVCH16260 Data Sheet