Features: ` 256 x 18-bit organization array (IDT72V205)

` 512 x 18-bit organization array (IDT72V215)

` 1,024 x 18-bit organization array (IDT72V225)

` 2,048 x 18-bit organization array (IDT72V235)

` 4,096 x 18-bit organization array (IDT72V245)

` 10 ns read/write cycle time

` 5V input tolerant

` IDT Standard or First Word Fall Through timing

` Single or double register-buffered Empty and Full flags

` Easily expandable in depth and width

` Asynchronous or coincident Read and Write Clocks

` Asynchronous or synchronous programmable Almost-Empty

and Almost-Full flags with default settings

` Half-Full flag capability

` Output enable puts output data bus in high-impedanc state

` High-performance submicron CMOS technology

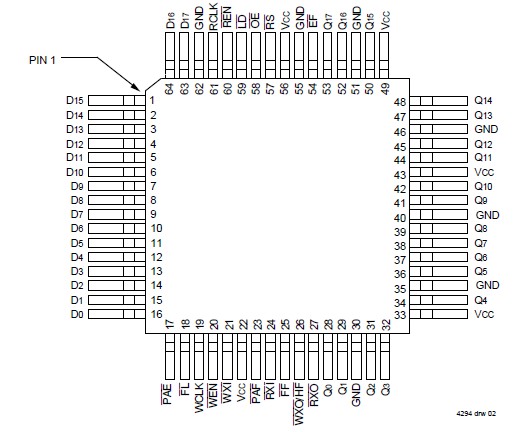

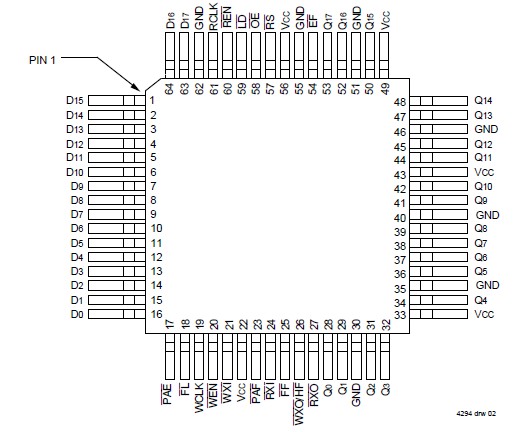

` Available in a 64-lead thin quad flatpack (TQFP/STQFP)

` Industrial temperature range (40°C to +85°C) is availablePinout Specifications

Specifications

|

Symbol |

Rating |

Commercial &Industrial |

Unit |

|

VTERM |

Terminal Voltage with Respect to GND |

0.5 to +5 |

V |

|

TSTG |

Storage Temperature |

-55 to +125 |

oC |

|

IOUT |

DC Output Current |

-55 to +50 |

mA |

NOTE:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent

damage to the device. This is a stress rating only and functional operation of the device at these

or any other conditions above those indicated in the operational sections of this specification is

not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. VCC terminal only.DescriptionThe IDT72V245 are functionally compatible versions of the IDT72205LB/72215LB/72225LB/72235LB/72245LB, designed to run off a 3.3V supply for exceptionally low power consumption. These devices are very high-speed, low-power First-In, First-Out (FIFO) memories with clocked read and write controls. These FIFOs are applicable for a wide variety of data buffering needs, such as optical disk controllers, Local Area Networks (LANs), and interprocessor communication.

These FIFOs of the IDT72V245 have 18-bit input and output ports. The input port is controlled by a free-running clock (WCLK), and an input enable pin (WEN). Data is read into the synchronous FIFO on every clock when WEN is asserted. The output port is controlled by another clock pin (RCLK) and another enable pin (REN). The Read Clock(RCLK) can be tied to the Write Clock for single clock operation or the two clocks can run asynchronous of one another for dual-clock operation. An Output Enable pin (OE) is provided on the read port for three-state contro of the output.

The synchronous FIFOs of the IDT72V245 have two fixed flags, Empty Flag/Output Ready (EF/OR) and Full Flag/Input Ready (FF/IR), and two programmable flags, Almost-Empty (PAE) and Almost-Full (PAF). The offset loading of the program mable flags is controlled by a simple state machine, and is initiated by asserting the Load pin (LD). A Half-Full flag (HF) is available when the FIFO is usedin a single device configuration.

There are two possible timing modes of operation with these devices: IDT Standard mode and First Word Fall-Through (FWFT) mode.

In IDT Standard Mode of the IDT72V245, the first word written to an empty FIFO will not appear on the data output lines unless a specific read operation is performed. A read peration, which consists of activating REN and enabling a rising RCLK edge, will shift the word from internal memory to the data output lines. mable flags is controlled by a simple state machine, and is initiated by asserting the Load pin (LD). A Half-Full flag (HF) is available when the FIFO is used in a single device configuration.

There are two possible timing modes of operation with these devices: IDT Standard mode and First Word Fall-Through (FWFT) mode.

In IDT Standard Mode of the IDT72V245, the first word written to an empty FIFO will not appear on the data output lines unless a specific read operation is performed. A read operation, which consists of activating REN and enabling a rising RCLK edge, will shift the word from internal memory to the data output lines.

In FWFT mode of the IDT72V245, the first word written to an empty FIFO is clocked directly to the data output lines after three transitions of the RCLK signal. A REN does not have to be asserted for accessing the first word.

These devices are depth expandable using a Daisy-Chain technique or First Word Fall Through mode (FWFT). The XI and XO pins are used to expand the FIFOs. In depth expansion configuration, First Load (FL) is grounded on the first device and set to HIGH for all other devices in the Daisy Chain.

The IDT72V245 are fabricated using IDT's high-speed submicron CMOS technology.

IDT72V245 Data Sheet

IDT72V245 Data Sheet